ここでは、米国Xilinx社のVirtex-ⅢProに内蔵されたハード・マクロのCPU (PowerPC)の使いかたを説明する。 開発フローを示し、ソフト・マクロのCPU (MicroBlaze)を使う場合と比較する。 また、同じ機能をハード・マクロとソフト・マクロで実現したときの性能比較も行う。 (編集部)

高集積化,高速化が急速に進んだFPGAの世界では,ソフト・マクロ<sup>注1</sup>のプロセッサが使われるのはもはやあたりまえになってきました.一方,ハード・マクロ<sup>注2</sup>のプロセッサは,それが搭載されたFPGAの製品数が少ないこともあり,これまであまり積極的には使われてこなかったようです.しかし,ASICの世界においては,「固定された回路なのでレイアウト設計の影響を受けず,高い性能が得られる」という利点もあって,ハード・マクロのIP(intellectual property)コアはよく使われているようです.

表1 汎用マイコンとハード・マクロ , およびソフト・マクロのプロセッサの比較

| 項目          | 汎用マイコン | FPGA<br>(ハード・マクロの<br>プロセッサ内蔵) | FPGA +<br>ソフト・マクロ<br>のプロセッサ |

|-------------|--------|-------------------------------|-----------------------------|

| 処理性能        |        |                               |                             |

| システムの柔軟性    |        |                               |                             |

| 高速クロックの使用   |        |                               |                             |

| アップグレードの容易さ |        |                               |                             |

| アーキテクチャの寿命  |        |                               |                             |

| 内蔵メモリ       |        |                               |                             |

| 評価環境        | ある     | ある                            | ある                          |

| デバイス単価      | 数百~数千円 | 数千~数十万円                       | 数百~数十万円                     |

は有利 , はやや有利 , は不利

これまで,汎用マイコンやASICに内蔵されるCPUコアとFPGA向けのソフト・マクロのCPUがよく比較されてきました<sup>(1)</sup>.今回は,FPGAに搭載されるハード・マクロのCPUとソフト・マクロのCPU,そして汎用マイコンを比較してみます(表1).

FPGAならではのシステムの柔軟性をある程度維持しながら高い処理能力を持てることがハード・マクロの特徴の一つです.とくに高速クロックについては,ハード・マクロ・プロセッサの高度な処理に必要な高い周波数の信号をFPGAの内部で利用し,外側のプリント基板上の回路では比較的低い周波数の信号を利用するといった構成をとれることがハード・マクロ・プロセッサを使う最大の利点であると筆者は考えます.

このように,ハード・マクロとソフト・マクロには一長一短があります.では,どのように使い分ければよいのでしょうか.もちろん目的によって使い分けるというのが最終的な答えになるかと思いますが,どちらを選択するかの一つの目安として,PowerPCコアを内蔵した米国Xilinx社のVirtex-Pro上にソフト・マクロのMicroBlazeを実装し,同じ処理を行わせて性能を計測する方法が考えられます.本稿ではこうした方法で,ハード・マクロとソフト・マクロのプロセッサの実力を比較してみたいと思います.

## 🔷 開発手順の比較

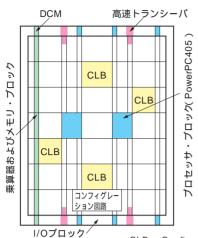

Xilinx社のVirtex- Proの概要を図1に示します.また,

注1: HDL記述やネットリストで提供されるIP( intellectual property )コア・ソフト・マクロのCPUには,FPGAベンダが提供するもの( 米国Altera社の「Nios」 か「Nios 」,米国Xilinx Xion「MicroBlaze」や「PicoBlaze」と,IPベンダが提供するもの( ローランの「AXAS」や米国CAST社の「C8051」など)がある.

や「Nios 」, 米国XIIInx 在の「MicroBlaze」や「PicoBlaze」)と、IPペンタが提供するもの(ローランの「AXAS」や米国にAST 在の「C805」など)かある. 注2:LSIのマスク・データとして用意されるIPコア・製造プロセスまで考慮して最適化されており、チップ上の実際の寸法や動作時のタイミングも確定している。FPGAにおいてハード・マクロというと,FPGAデバイスにあらかじめ組み込まれている,基本論理プロック以外の大規模回路プロックを意味する.ハード・マクロのCPUとしては,例えばXilinx社のVirtex-ProやVirtex-Pro、Virtex-4 FXに内蔵されたPowerPCコアがある.

| 型名       | 高速<br>トランシーバ | PowerPC<br>コア | 論理セル   | スライス   | 18×18<br>ビット<br>乗算器 | 18Kビット・<br>メモリ・<br>ブロック | DCM |

|----------|--------------|---------------|--------|--------|---------------------|-------------------------|-----|

| XC2VP2   | 4            | 0             | 3,168  | 1,408  | 12                  | 12                      | 4   |

| XC2VP4   | 4            | 1             | 6,768  | 3,008  | 28                  | 28                      | 4   |

| XC2VP7   | 8            | 1             | 11,088 | 4,928  | 44                  | 44                      | 4   |

| XC2VP20  | 8            | 2             | 20,880 | 9,280  | 88                  | 88                      | 8   |

| XC2VPX20 | 8            | 1             | 22,032 | 9,792  | 88                  | 88                      | 8   |

| XC2VP30  | 8            | 2             | 30,816 | 13,692 | 136                 | 136                     | 8   |

| XC2VP40  | 0,8,12       | 2             | 43,632 | 19,392 | 192                 | 192                     | 8   |

| XC2VP50  | 0 , 16       | 2             | 53,136 | 23,616 | 232                 | 232                     | 8   |

| XC2VP70  | 16 , 20      | 2             | 74,448 | 33,088 | 328                 | 328                     | 8   |

| XC2VPX70 | 20           | 2             | 74,448 | 33,088 | 308                 | 308                     | 8   |

| XC2VP100 | 0,20         | 2             | 99,216 | 44,096 | 444                 | 444                     | 12  |

(b)ファミリの概要

CLB : Configurable Logic Block (a) ブロック図 DCM : Digital Clock Manager

## 図1 Virtex- Proの概要

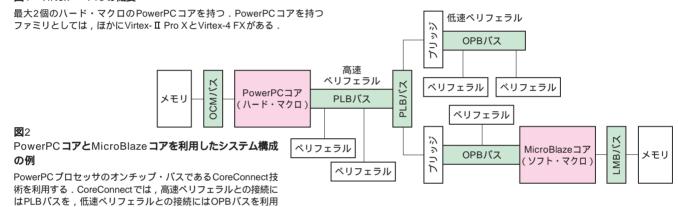

Virtex- Proの内部に構成するプロセッサ・システムのバス構造は図2のようになります。まず、PowerPCシステムでは、PowerPCコアとローカル・メモリの間をOCM(Onchip Memory)バスで、PowerPCコアとペリフェラル(外付けメモリのコントローラや入出力インターフェース回路など)の間をPLB(Processor Local Bus)バスで接続します。MicroBlazeシステムでは、MicroBlazeコアとメモリの間をLMB(Local Memory Bus)バスで、MicroBlazeコアとメモリアとペリフェラルの間をOPB(On-chip Peripheral Bus)バスで接続します。MicroBlazeシステムとPowerPCシステムの間は、PLBバス、バス・ブリッジ、OPBバスを介して接続します。

する.ソフト・マクロのMicroBlazeコアはOPBバスに接続する.

## ● PowerPCシステムを開発する

Virtex- Proに搭載されているPowerPCコアを使うシステムの開発には, Xilinx社の「Embedded Development Kit(EDK)」を使用します.まず, EDKのBase System

Builder(BSB)ウィザードを使用して,ターゲットFPGAの基本的な構成を組み立てます. Base System Builderを含めた開発のフローの概略を図3に示します.

EDKが備える組み込みシステム開発ツール「Platform Studio」で白紙の状態から作成することももちろんできますが、PowerPCコアとリセット回路の接続など、信号線が多くかつミスをすると回路がまったく動作しないおそれのある部分は、ウィザードで自動的に接続してもらうのが賢明です。さらに、EDKのバージョン6.3からは、独自設計のボードでもこれらの基本的な接続が行えるようにBase System Builder(BSB)が機能強化されました。

Base System Builderは一度に一つのプロセッサしか選択できないので、まず、構成がより複雑なPowerPCプロセッサのペリフェラルを作成し、のちに手動でMicroBlazeの回路を追加します、したがって、まず、図3のフローのの直後に判定する「追加コアなし」をYESとします、次に、、を実行せず、Base System Builderのデフォルト設定でシステムをビルドします。