SATA ホストの動作や仕組みを事例で解説

# FPGA でハード・ディスクを 制御してみた

大牧正知

筆者はFPGA ボードを使ってハード・ディスクを制御する装置 を自作した. 設計したのは主にFIS (Frame Information ある Micro Blaze を使用した. ここでは本製作事例を使って、

Structure) と呼ばれるデータをメイン・メモリに作成し、リ ンク層に相当するブロックに転送するような FPGA デザインで ある. 物理層は FPGA の高速トランシーバで、リンク層は SATAのIP (Intellectual Property) コアで、トランスポー ト層はVHDL 記述などで実現し、全体の制御にはCPU コアで

内部バス HDD SATA SATA CPU コントローラ DMA (Direct DDRメモリ メモリ など コントローラ Memory Access (a) SOC内蔵

PCI, PCI-X, チップセット SATA SATA CPU など 制御厂 PCI Express などのバス DDRメモリ など

(b) 外付けSATA制御IC

(c) 変換IC

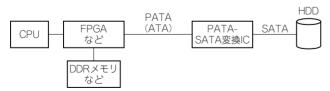

図1 組み込み機器における SATA 実現例

SATAホストの動作や仕組みを解説する、本稿で掲載する VHDL やC言語のソース・ファイルは本誌 Web サイト (http://www.cqpub.co.jp/dwm/) からダウンロードでき る. (編集部)

## 1. SATA ホストのハードとソフト

● 組み込み機器でSATAを実現するためのハードウェア 組み込み機器でSATA を実現する場合,大きく分けて以 下に示すようなハードウェア構成が考えられます(図1).

#### (1) SATA 内蔵の CPU (SOC) を使う場合

米国 AMCC (Applied Micro Circuits Corporation) の 「PPC460EX | や米国 Freescale Semiconductor 社の「MPC 8379E | などのCPUは、1チップでSATAインターフェー スを備えています. これらを使えばそのままSATA が使え るので簡単です.

これらのCPUの欠点としては、比較的値段が高いこと と、5チャネル以上のSATAポートを持っているデバイス が少ないことがあります。また、多くの CPU はハード・ ディスクを制御する側である SATA ホスト機能が内蔵され ており、制御される側のSATA デバイス機能はほとんど内 蔵されていません.

#### (2) 外付け SATA コントローラ IC を使う場合

米国 SiliconImage 社や米国 Marvell Technology 社など から、PCIやPCI-X、PCI Express 接続のSATA 制御(コ ントローラ) IC が提供されています。ホスト・プロセッサ がSATA制御ICで使われているバス・インターフェース

Keyword

SATA コントローラ、トランスポート層、リンク層、物理層、ホスト、デバイス、FIS、DMA 転送、MicroBlaze。 VHDL, C言語, IDENTIFY DEVICE, DMA READ EXT, DMA WRITE EXT

## **ハード・ディスク**を使った 集 ストレージ入門

を持っていれば、そのままつなぐだけで使用できます。

欠点としては、システム・コストが高くなってしまうこ とです、PCIではSATAに対して十分な帯域がないので、 PCI-X やPCI Express のバス・インターフェースを持った 製品が多いのですが、これらのインターフェースを持った CPU は比較的値段が高くなるからです。また、これも SATA デバイスの機能を持っているものは少ないようです.

#### (3) PATA-SATA 変換チップを使う場合

従来のPATA(ATAのこと)のインターフェースに、 PATA-SATA 変換チップを接続して、SATA を実現でき ます。この方法だと従来のソフトウェアがそのまま使えま す. 設計資産をそのまま流用できるので簡単です. また. PATA-SATA 変換チップはかなり安くなってきており、シ ステム・コストも低く抑えられます。PATA-SATA変換 チップは、SATAデバイス側にも使用できます.

欠点は、1.5Gbps まで(実際は Ultra DMA モード5の 133M バイト/s まで) の速度しかサポートできないことと, 多チャネルになると基板上の配線が増えてしまう(1チャネ ル当たり30本程度)ことです。

#### (4) FPGA に SATA の IP コアを実装する場合

そのほか、FPGAにSATAのIPコアを入れて実現する という方法があります. これはSATA内蔵のCPU(SOC) を使う場合と近い形になります。SATAデバイスとしても 使用できます、本稿では、この方法でSATA を実現する方 法について解説します.

#### ● FIS というデータを使って SATA デバイスにアクセス

SATA 内蔵 CPU を使う場合や外付けの SATA 制御 IC を 使う場合と、PATA-SATA変換チップを使う場合とでは、 ソフトウェアが大きく異なります.

PATA-SATA 変換チップを使う場合は、従来のPATA を使うときとソフトウェアはなんら変わりません. SATA 内蔵CPUを使う場合や外付けSATA制御ICを使う場合 は、通常FIS (Frame Information Structure) と呼ばれる データ構造を用いてアクセスします.

ハード・ディスクなどのSATA デバイスにアクセスする ときは、FISデータを作成し、SATAコントローラに送信 します。一般的にはメイン・メモリ上に FIS データを作成 し、コントローラがバス・マスタになってそのFISデータ を読み取り、SATAデバイスへ送信するようです。

SATA デバイスから受信したFIS データは、SATA コン

トローラがバス・マスタになり、メイン・メモリに展開し ます.

従って、ホスト・プロセッサは、以下のような手順で SATA デバイスへアクセスを行うことになります.

#### (1) FIS データの作成

(初めはホストからデバイスにデータを渡すRegH2Dコ マンドを作成)

- (2) FIS データの送信

- (3) FIS データの受信待機

- (4) 受信した FIS データを読み出し

- (5) 必要に応じて FIS の送受信

プロトコルによって送受信するFISの数などが異なって きますが、おおむねこのような流れになります.

### 2. SATA ホストを FPGA に実装

#### ● SATA IP コアはリンク層のみの場合が多い

FPGA あるいは ASIC (Application Specific Integrated Circuit)でSATAを実現する場合、ゼロから作るのは大変 なため、IPコアを使用することが多いかと思います。現在 提供されているSATA IPコアは、リンク層部分のみで、 物理層やトランスポート層を含んでいない場合が多いよう です。

物理層は、デバイス自体の作りこみにより制御方法が異 なってくるほか、ホストとデバイスでも動きが異なります。 トランスポート層は、上位との接続方法やアプリケーショ ンで作りが異なるため、IPコア化しにくいものと思われます。

#### ● FPGA 高速トランシーバと接続できる IP コアを採用

米国 Xilinx 社の FPGA の場合、 Virtex-5 LXT/SXT/ FXT などを用いると、物理層も含めてSATA を実現でき ます。同社のWebサイトからは、SATAホスト用の物理 層のサンプル・デザイン (XAPP870) がダウンロードでき るほか、SATAの特性レポート(rpt087)も入手でき、参 考になります.

SATA IP コアはいくつかの IP ベンダからリリースされ ています. 今回はデザイン・ゲートウェイのSATA IPコ アを使用した事例を紹介します。一般的なSATA IPコア のPHY (物理層)との接続は、sapisと呼ばれるインター フェースを用いています. 本IPコアはVirtex-5 LXT/SXT の高速トランシーバ (GTP) 向けに最適化されています。物