## 第2章 スキャン設計、 バウンダリ・スキャン, そしてBIST

～JTAGを使ったLSIテスト回路の組み込み手法～

古川 寛

JTAG自体は、もともとはボード・テストを目的とした技術である。また、LSIの設計ではスキャン設計が行われ、そのための回路が組み込まれている。この二つのスキャンは前者が外部スキャン、後者が内部スキャンと呼ばれ、別々の技術であった。ここでは、この二つの技術を組み合わせてLSIをテストする手法を紹介しよう。後半は最近注目されているテスト回路に関する話題としてBISTを取りあげる。

(筆者)

### 1.スキャン・パス・テストの問題点

#### ■スキャン・パス・テスト機能をICに組み込むには

LSIのテスト容易化設計(design for testability)手法として、よく利用されているものにスキャン設計がある。これは論理回路中の順序回路にテスト・モード用のパス(スキャン・パス)を通して制御し、一つのシフト・レジスタとして動作させる方法である。

具体的には、内部(コア・ロジック)のすべてのフリップフロップ(レジスタ)のデータ線にマルチプレクサを追加する(フ

ルスキャンの場合)。これをスキャン・フリップフロップと呼ぶ。スキャン・フリップフロップを数珠つなぎに接続して、巨大なシフト・レジスタを構成する。このシフト・レジスタ(スキャン・パス)を利用して、コア・ロジックのフリップフロップに対して、直接、値を書き込んだり、値を読み出したりする(シフト・レジスタを使ってアクセスする点はバウンダリ・スキャン手法とよく似ている。詳細は後述)。たとえばATPG(自動テスト・パターン生成)ツールによって生成したテスト・パターンの故障検出率(fault coverage)が上がりにくい場合でも、スキャン設計を適用すると、故障検出率の高いテスト・パターンを得やすくなる。

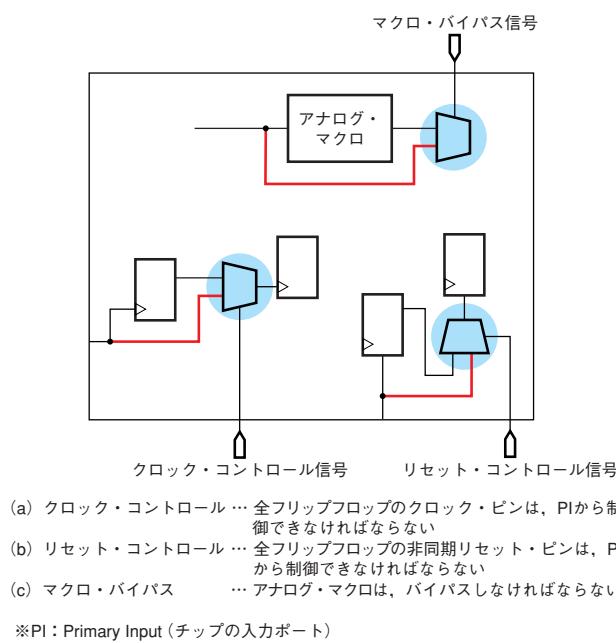

LSI設計者が、スキャン・パス・テスト機能(ここでは主にフルスキャン)をLSIに組み込もうと考えた場合、いくつかの設計制約がある。これらは、

- (1)クロック制御に関する制約

- (2)リセット制御に関する制約

- (3)アナログ・マクロに関する制約

- に代表される(図1)。

(1), (2)はスキャン・パス・テストが本来、フル・ロジックの単相同期式設計のテスト手法であるためであり、(2)はスキャン・シフト中にフリップフロップの値が壊されないようにというためである。(3)については、アナログ・マクロはテストの対象外になるため、バイパスしなければならない。

通常、スキャン・パス・テストを適用するためには、これらの

[図1] スキャン・パス・テストの設計制約

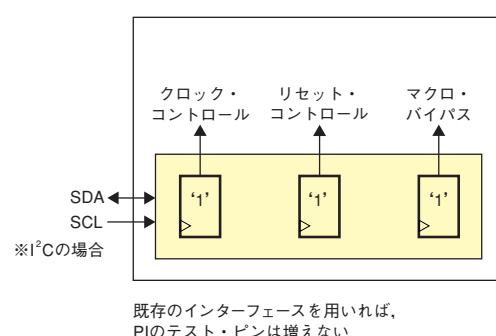

[図2] レジスタによるテスト・モード設定

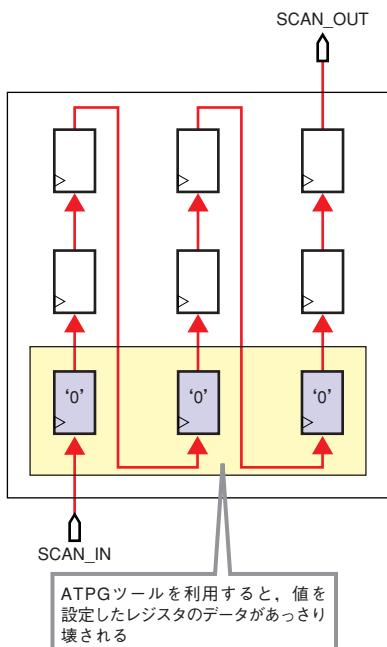

[図3] テスト・モード・レジスタのデータ破壊

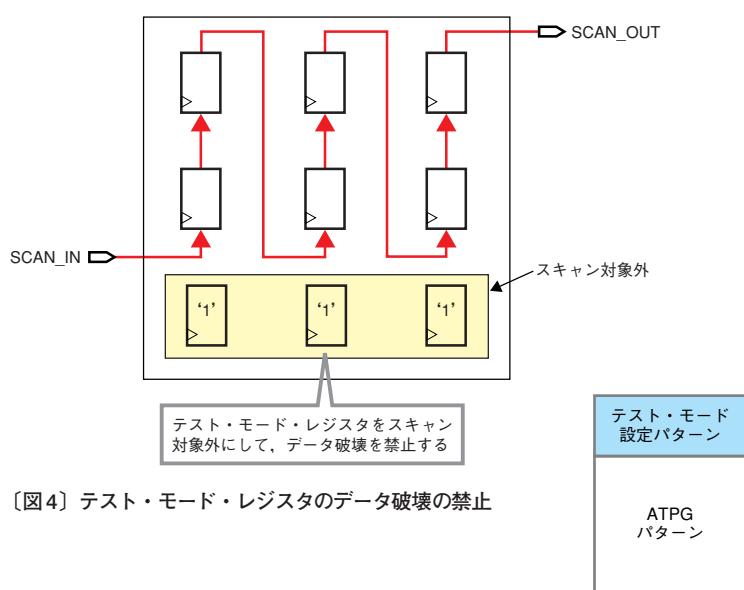

[図4] テスト・モード・レジスタのデータ破壊の禁止

[図5] テスト・モード設定パターン+AATPGパターン

制約を遵守して回路として作り込まなくてはならない。そこで各信号は、すべてPI(Primary Input)で制御することになる。

### ■ 2ピンのポートでスキャン・パス・テストはできないか?

ここで問題は、PIにおいてテスト・ピンを用意する必要があるということである。これが、ときおりネックになる。製品の都合上、ピン数に制約を受ける場合である。

それでは、スキャン・パス・テストではない通常のテスト・モード切り替えはどうしているのか? 既存(I<sup>2</sup>Cバスなど)もしくは専用のシリアル・インターフェース(別にパラレルでもよいが)を用いて2ピンくらいで内部レジスタに値を設定する方法が考えられる(図2)。

このような手法、つまりシリアル・インターフェースを使って内部レジスタに値を設定した後、AATPGを行うような方法が、スキャン・パス・テストでも使えないのだろうか? 残念ながら、この手法はスキャン・パス・テストでは使えない。

というのは、全フリップフロップがスキャン・チェーンに接続されてスキャンされるために、AATPGツールで生成したテスト・パターンがフリップフロップの値をどんどん壊して(書き換えて)しまい、設定した状態を保持できないからである(図3)。これを回避するには、テスト・モードを決定する内部レジスタをスキャン・フリップフロップに置換しなければよい(図4)。こうすれば、テスト・モードの状態を保持させた状態でAATPGを適用できる。

ただし、以下の2点の問題がある。

- (1) スキャン化しない部分は、テスト・モードを決定している内

部レジスタだけでなく、その周辺回路も含める必要がある。

(2) パターン・マージが必要になる(図5)。

(1)でその周辺回路を含める理由は、フリップフロップに値を設定した後、値が書き換えられないようにするためである。そのためその範囲は回路に依存し、限定することはむづかしい。(1)で問題となるのは、AATPG対象外の部分が広範囲におよんだ場合に故障検出率が低下すること、またその対象外の部分を別の方法でテストする必要があることである。

(2)の問題では、テスト・モード設定用の手作りのテスト・パターンとAATPGで生成したテスト・パターンをマージする必要がある。しかし、それがうまくいくという保証はない。

詳細なタイミングまで考慮すればAATPGを使うだけでも実現可能だろうが、イレギュラなことにはかわりないので、現状ではほとんど用いられていない。

## 2.スキャン・パス・テストとJTAG

さて、最近の大規模LSIではバウンダリ・スキャン用のJTAGインターフェース回路を組み込む例が増えている。バウンダリ・スキャンとは、現在、おもにボード・テストで利用されているテスト容易化設計手法である。内部のコア・ロジックと入出力ピンの境界にバウンダリ・スキャン・レジスタ(バウンダリ・スキャン・セル)を配置し、これらを数珠つなぎに接続してシフト・レジスタを構成する。シフト・レジスタ(シリアル・ポート)の制御には、TAP(Test Access Port)コントローラと呼ぶ回路を利用する(詳しくは本特集の第1章を参照)。