# 設計者に必要な テスト工程の基礎知識

— LSI テスターを理解してテスト設計の方針を決める

加賀博史

ここでは、LSI テストの概要について説明する。LSI テスターは、1台が数千万～数億円もする高価な装置である。テスト時間がのびると、それだけテスト・コストが上昇する。また、適切なテスト対策を施さず、高級な LSI テスターでないとテストできないような回路を設計してしまうと、さらにテスト・コストが上がる。チップ面積をどんなに小さくしても、テスト・コストが上昇してしまっては意味がない。ここでは設計者に必要なテスト工程の基礎知識について解説する。また、LSI 設計者がテスト技術者と協力して検討すべき項目について説明する。

(編集部)

LSI 設計・製造の全工程中、テストは他の工程のエンジニアからもっとも疎まれている工程かもしれません。これは、テスト工程には高額な設備投資が必要であるのに対して製品の付加価値を生むことが原則的ないこと、またテスト工程の存在そのものが他の工程の作業に欠陥があることを前提としていることに起因していると思います。

本来、設計と製造プロセスが完璧であるならば、テスト工程は不要なはずです。テスト工程が有効に機能するということは、すなわち、設計が製造プロセスのどちらかに欠陥があることの証明なのです。プロセス技術者の立場から見ると、テスト技術者は自分たちの苦労の結晶であるウェハやパッケージに不良品のらく印を押す連中であり、回路設計者の立場から見ると、苦心して設計した回路なりアーキテクチャなりに不備があることを最初に見つける憎いやつらというわけです。

多くの場合、設計工程も製造工程もぎりぎりの日程で進行しています。そのため、最終工程のテストにおいて

チップが動作しないことが報告されようものなら、他の工程にたずさわるエンジニアたちは、えてしてこの事実を認められないという感情が先に立ち、LSI テストのあら探しを始めたりします。このため、テスト技術者は自分の仕事の正当性を他のエンジニアに証明することに多くの時間を消費させられます。自分たちこそ IT (information technology) 社会の基盤を支えていると自認する誇り高い回路設計者や、いまや原子の世界をも制御しているプロセス技術者を相手に戦っていかなければならぬのですから、これはたいへん骨の折れる仕事です。経験を重ねたベテランのテスト技術者に、(あくまでも仕事上の話ですが… ) 攻撃的な性格の人が多いのは、このためかもしれません。

しかし、先端のシステム LSI などのチップの開発では、設計段階から量産に至るまで、設計者とテスト技術者が協力して仕事を進めていかなければならない局面が急増してきています。LSI 設計者とテスト技術者の間の相互理解がなければ、LSI を開発できなくなってきたといっても過言ではありません。ここでは、LSI の設計にたずさわる方を対象に、LSI のテスト工程を理解していただくことを目的に、その基礎を解説します。

## 1 テスト工程の基礎知識

LSI を製造・出荷するために行うテストは、DC (直流) テストと AC (交流) テストに大別されます。DC テストはチップの静的特性を確認するもので、主として入出力バッファの電圧・電流特性を保証するためのものです。これに対して AC テストはチップの動的特性を確認するもので、主として LSI に組み込まれた機能 (ファンクション)

を保証するためのものです(なお、本稿ではストラクチャ・テストも機能テストに含めて説明する)。

昨今、半導体製造技術の微細化の進展によりLSIに集積される回路規模が飛躍的に増大しています。このため、LSIの外部からLSIの内部に組み込まれたすべての機能をテストすることがきわめて困難となってきており、テストを容易にするための回路設計が必要となってきています。この状況に対応するため、さまざまなテスト容易化設計(DFT: design for testability)技術が開発されています。現在のところ、DFT技術は品質の高い機能テストの実現を目指しています。

表1に、DCテスト、ACテストの例を示します。テストするチップに組み込まれた機能や、要求される品質によって、必要なテストを取捨選択して実行する必要があります。

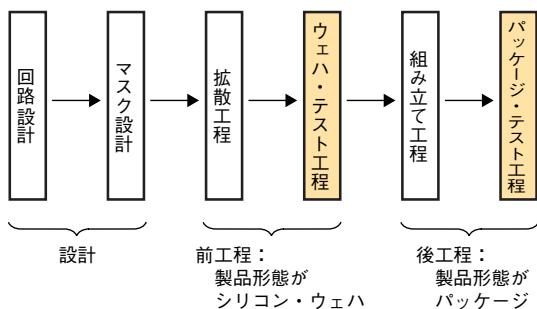

実際の半導体製造工程では、これらのテストをウェハとパッケージの2段階で実施することが一般的です。LSIの設計から製造までのフローを図1に示します。

[図1] 設計・製造工程のフロー

製造工程中、テスト工程はウェハ・テストとパッケージ・テストの2段階で行うのが一般的である。それぞれ、拡散工程、組み立て工程でつくり込まれた不良品の除去を目的としている。フロー全体でテスト品質を最大に、テスト・コストを最小にするよう、フローを構成する必要がある。

[表1] ロジックLSIのテスト項目

|                       | テスト項目                     | テストの内容                       |

|-----------------------|---------------------------|------------------------------|

| D<br>C<br>テ<br>ス<br>ト | オープン(開放)テスト、ショート(短絡)テスト   | 信号端子、電源端子のオープン不良、ショート不良のチェック |

|                       | $I_{OL}, I_{OH}$ テスト      | 出力バッファ電流チェック                 |

|                       | $V_{OL}, V_{OH}$ テスト      | 出力電圧チェック                     |

|                       | $I_{IH}, I_{IL}$ テスト      | 入力バッファ・リーク電流チェック             |

|                       | $V_{IH}, V_{IL}$ テスト      | 入力電圧マージン・チェック                |

|                       | 静的 $I_{DD}$ テスト           | 電源電流チェック(LSIの静止時)            |

| A<br>C<br>テ<br>ス<br>ト | LFT (loose function test) | 機能テスト(低周波数)                  |

|                       | アット・スピード・テスト              | 機能テスト(実動作周波数)                |

|                       | スキャン・テスト                  | DFT 対応ストラクチャ・テスト             |

|                       | BIST                      | DFT 対応機能テスト                  |

|                       | コア分離テスト                   | DFT 対応機能テスト                  |

|                       | $I_{DDQ}$ テスト             | (DFT 対応) 故障電流チェック            |

|                       | 電源電圧マージン・テスト              | LSIの電源電圧変動耐性チェック             |

|                       | 動的 $I_{DD}$ テスト           | 電源電流チェック(LSIの動作時)            |

## ●ウェハ上のチップをテストするウェハ・テスト

ウェハ・テストは、拡散工程で製造されたウェハ上のチップに対して、前述のテスト項目より必要なテストを選択して実施し、正しく動作するチップ(良品)とそうでないチップ(不良品)を識別します。この工程には主として次の二つの目的があります。

b ウェハ上のチップの良品/不良品を識別することによって、後工程(組み立て工程)で良品のみを組み立てる。

b 不良項目を拡散工程にフィードバックし、これを解析する。歩留まり低下の要因を分析し、対策を施す。

次に、ウェハ・テストを実施するために必要な装置と治具について説明します。

### (1) LSI テスター

LSI テスターはテスト工程の主役となる装置です。基本的には、テスト対象となるチップ(DUT: device under test)に入力信号を印加し、出力信号を検知します。これをあらかじめ設定された期待値(仕様)と比較することによって、良品/不良品の判定を行います。その機能と、対象とするチップに対応して、以下の4種類に分類されます。

b ロジック・テスター——ロジックLSIのAC/DCテストを行うLSI テスター

b メモリ・テスター——メモリLSIのAC/DCテストを行うLSI テスター

b ミックススト・シグナル・テスター——LSIのアナログ機能のテストを行うLSI テスター(pp.44-46のAppendix「設計者に必要なミックススト・シグナル・テストの基礎知識」を参照)。

b SOC テスター——上記3種類の機能を組み合わせた汎用テスター