# Appendix IDDQ テストの故障モデル

# 安藤至誠

現在のLSIテストでは、縮退故障を想定してテストすることが多い、縮退故障とは、論理値が'0'または'1'に固定される故障である。しかし、現実には縮退故障モデルでは対応できない欠陥も少なくない、たとえばショート(短絡)故障やオープン(開放)故障などである。ここでは、こうした物理的な故障を検出できる loog テストの概要を紹介する。なお、本稿に登場する loog テスト用故障シミュレータ [TDX-IDDQ]の評価版を本誌 2001 年 5 月号(4 月 10 日発売)の付属 CD-ROM に収録する予定である。(編集部)

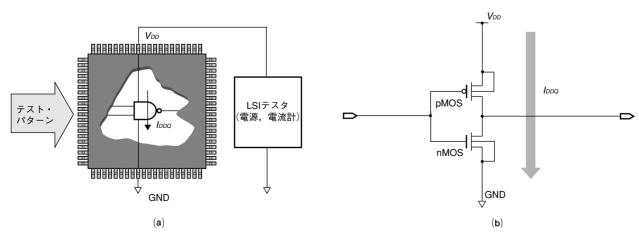

$I_{DDQ}$  テストは、CMOS 回路の故障を見つけるためのテスト手法です。CMOS 回路では、トランジスタがスイッチング動作をしていない静止時に、チップの電源電流  $I_{DD}$  がごくわずかしか流れません (静止時のリーク電流は  $\mu$  A  $\sim$  nA). ところがチップに故障が発生すると、大きな電流が流れます。この現象に着目し、静止時の電源電流を測定して故障の有無を判別する手法が  $I_{DDQ}$  テストです (図1)。  $I_{DDQ}$  のQは  $\Gamma$  quiescent (静止状態の)」を意味しています。

$I_{DDQ}$  テストは、CMOS 回路であれば、同期回路でも、非同期回路でもテストできます。従来の縮退故障に加えて、オープン(開放) 故障やショート(短絡) 故障、複合故障なども検

出できます。また、比較的少数のテスト・パターンで多くの 故障を検出できるという特徴があります。

ただし、 $I_{DDQ}$ テストにはテスト速度が遅い(電流が静止状態になるまでの待ち時間が必要になる)、電源電圧が低くなってくると測定がむずかしくなる、などの課題があります。現状の $I_{DDQ}$ テストは、あくまでも機能(ファンクション)テストやスキャン・テストによるテストの抜けを補うための手法と言えます。

ここでは、まず $I_{DDQ}$  テストの原理について解説します。その後、 $I_{DDQ}$  テストの故障モデルの例として6ショート・トランジスタ・モデルを紹介します。

### ●観測用検査点を挿入する必要がない

CMOS 回路は、電源  $V_{DD}$  に接続される pMOS素子と、GND に接続される nMOS素子を組み合わせて構成されます。 入力が与えられた場合、pMOS素子と nMOS素子のいずれか一方だけが ON 状態となります。定常状態では回路に電流がほとんど流れませんが、不良があると電流レベルは通常の何倍にもなります。電源電流を観測するだけで故障を検出できるので、いわゆる可観測性に対する配慮は不要です。可観測性を引き上げるために、検査点の挿入などを行う必要はあ

〔図1〕 *IDDQ* テスト

LSI に故障があると、トランジスタがスイッチング動作をしていないとき、大きな電源電流 ( $I_{DOO}$ ) が流れる。これを測定して故障の有無を判別する手法が  $I_{DOO}$  テストである。リーケージ・テストとも呼ばれる。

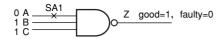

#### 〔図2〕縮退故障

論理値が '0' または '1' に固定されてしまう故障。図では3 入力 NAND の入力 A が '1' に固定された場合を想定している。テスト・パターン"011"が入力されても、出力 Z が '0' になる。

#### りません.

故障検出では、なんらかの物理的原因によって、回路要素が正常時と同じ論理出力を得ることができなくなった状態を仮定します。故障シミュレーションで使用される故障モデルは、おもに図2のような縮退故障モデルです。これは論理値が'0'または'1'に固定される故障です。

現在の故障検出において実用的なモデルとして広く利用されているのはこの縮退故障モデルですが、このモデルだけでLSIのすべての故障を検出することはできません。たとえば、縮退故障モデルをもとに作成したテスト・パターンを使って、ショート故障やオープン故障を100%検出できる保証はありません(ただし、経験的には縮退故障モデルによる故障検出率を上げると、その他の物理的故障も検出されやすいとされている).

## ●縮退モデルで対応できない等価故障と冗長故障

一般的な論理ゲート・レベルの故障モデルにおいて、注意 する必要があるものとして、等価故障と冗長故障があります。 等価故障とは、テスト対象となるチップに適当な入力を 与えたとき、正常時と異なる出力になるものの、つねに同じ

出力になるため、互いに他の故障と区別がつかないという故障です。 一方、冗長故障はテスト対象となるチップに対して、どの

一方, 冗長故障はテスト対象となるチップに対して, どのようなテスト・パターンを入力してもその存在が検出できない故障です。 実際のLSI設計では論理上のクリティカル・パスを改善するために冗長な回路構成にする場合が少なからずあります。 こうした箇所に不良が発生すると, 機能動作上の仕様は満たせても, 動作速度が未達になるという問題が出てきます。 冗長故障は各ノードが'0'または'1'に固定されることを仮定する縮退故障モデルでは検出できません。 冗長故障が存在すると, 動作性能が低下する場合が多いことに注意する必要があります。

以上の観点から、より高い信頼性を保つには、縮退故障モデルだけではむずかしいと言えます。縮退故障以外の不良を検出して、高い信頼性を保つためのテスト技術の一つが $I_{DDQ}$ テストなのです。

→₩→:ショート故障の発生場所

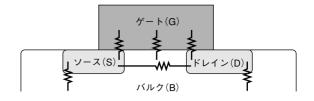

#### 「図3〕6ショート・トランジスタ・モデル

6ショート・トランジスタ・モデルは、CMOS 回路内の各トランジスタのゲート、ソース、ドレイン、バルクの間のショート故障を表現したモデルである。具体的には、「ゲートとソースの間のショート」、「ゲートとドレインの間のショート」、「バルクとソースの間のショート」、「バルクとドレインの間のショート」、「バルクとゲート間のショート」の6種類がある。

## ●トランジスタ・レベルのショート故障モデルの例

$I_{DDQ}$  テストでは、さまざまな故障モデルを考慮することができます。ここではそれらのうち、市販の故障シミュレータがサポートしているショート故障モデルの例を紹介します。ここで説明するのは、6ショート・トランジスタ・モデルと呼ばれているものです。

6ショート・トランジスタ・モデルは、トランジスタ・レベルのショート故障のモデルです。CMOS 回路内の各トランジスタのゲート(G)、ソース(S)、ドレイン(D)、バルク(B)の間のショート(短絡)を表現します。具体的には、以下の6種類のショートが考えられます(図3)。

- b ゲートとソースの間のショート

- b ゲートとドレインの間のショート

- b ソースとドレインの間のショート

- b バルクとソースの間のショート

- b バルクとドレインの間のショート

- b バルクとゲートの間のショート

ここで、図4のようなCMOS 回路の3入力 NAND ゲートを考えてみましょう。3入力 NAND ゲートは3個のpMOSトランジスタと3個のnMOSトランジスタから構成されています。それぞれのトランジスタについて、上記の6種類のショートが考えられます。つまり、3入力 NAND ゲート全体では、合計 $6\times 6=36$  個のショート故障が考えられます。ただし、トランジスタが電源  $(V_{DD})$  やGND と接続されている4箇所(図4の①~④)については、バルクとソース(またはドレイン)の間のショートを検出できません。つまり、3入力 NAND ゲートにおいて検出可能な故障の数は32個となります。

3入力 NAND ゲートの6 ショート・トランジスタ・モデルは、たとえば米国 Fluence Technology 社の $I_{DDQ}$  テスト用故障シミュレータ「TDX-IDDQ」の場合、リスト1 のように記述します<sup> $\pm$ </sup>. リスト1 の各行の左端にある"000"~"111"は、3入力 NAND ゲートの入力値に相当します。