# GHz ディジタル回路の電源デカップリングと信号配線の設計法

—電磁気学の基本に立ち戻って高速ディジタル回路を設計する—

遠矢弘和

ここでは、ノイズの影響を考慮した高速ディジタルLSIや高速ディジタル・ボードの設計法を紹介する。具体的には、電源デカップリングと信号配線についての新しい考え方を紹介する。GHzオーダの高速ディジタル回路の設計では、電磁気学の基本に立ち戻り、配線を伝搬する信号を電磁波とみなして設計する必要がある。筆者らは、こうした回路に適した低インピーダンス線路素子も開発している。

(編集部)

今やディジタル技術は電子機器に広く採用されており、性能を引き上げるため、いっそうの動作速度向上が望まれています。こうした機器の設計では、高速化と電磁干渉の抑制を両立させなければなりません。これまで以上に高速なディジタル回路を実現するには、電磁気学の基本に立ち戻り、配線を伝搬する信号を電磁波とみなすことから始めるべきであると筆者は考えています。

電源分配品質を改善するには電源デカップリングが重要です。筆者らはGHz以上で動作する高速ディジタル回路に適した低インピーダンス線路素子(LILC: low impedance line structure component)を開発しました。これは、従来のコンデンサでは実現不可能な高周波の領域まで十分低いインピーダンス特性を有するユニークな素子です。

また、新しい配線設計法も開発中です。これは、CMOS LSI内部、およびCMOS LSIを搭載したボード上の配線を対象とした配線手法です。基本的には、CMOSトランジスタのスイッチング動作を配線容量とゲート容量の電磁波による充放電とみなし、抵抗成分を利用して最適な充放電条件に設定します。この方法を利用すると、ボード上であっても、6GHz以上の高速ディジタル信号を受け渡すことができます。同一のクロック周波数で比較した場合、クロストーク・ノイズなどの電磁干渉やEMI(electromagnetic interference)、消費電力を従来より大幅に低減できると考えています。

本稿では、筆者らが開発しているこうした電源デカッ

プリングと信号配線に関する新しい設計法を紹介します。

## ◆電源デカップリングの強化でEMI問題を解決

筆者は、メインフレーム(大型汎用コンピュータ)の回路技術の開発に約25年携わった後、従来の方法では歯が立たないEMC(electromagnetic compatibility)問題を解決するために研究所に移り、約9年が経過しました。当初はEMC規格に適合する機器の設計手法を目的として研究を行っていましたが、その後、研究対象を徐々にディジタル回路における電磁干渉の根本原因の究明に移してきました。このようなスタンスで研究を進めるうちに、LSIの電源端子からプリント基板に漏れ出る高周波電源電流が電磁干渉の大きな原因であることを突き止めました。

この過程を簡単に説明します。まず、出荷中のワークステーション製品をはじめとする多くのディジタル電子機器を対象に、電源デカップリングの強化を試行しました。具体的には、LSIに電源を供給する電源分配回路をブレーン(平板)からの配線にして、インダクタンスとコンデンサで構成したローパス・フィルタを使用して電源デカップリングを強化しました。試作を行って評価したところ、以下のような事実を確認しました<sup>1)~4)</sup>。

- 装置からの放射電界強度が、広い範囲で10dB以上抑制される

- 電磁界放射への高周波電源電流の寄与度が、信号系よりも格段に大きい

- ノイズの低減だけでなくイミュニティの向上にも大きな効果がある

- 信号線に使用しているEMC対策部品が不要になる

以上のような事実から、デジタル機器のEMC問題について、以下で述べる二つのことが考えられます。

- 1) CISPR(国際無線障害特別委員会)の規格に基づくEMI規格適合確認テストでは、ほぼクロック成分のみを測定している

これは、以下の理由によります。

- 周期成分しか測定できない妨害波測定器やスペクトラム・アナライザを指定している(IEC/CISPR16)。

- 間欠性(非周期性)妨害波の読み取り値は除外できる(IEC/CISPR22)。

- クロックに変調をかける、いわゆるスペクトラム拡散を利用すると、容易に規格をクリアできる。

- 2) 電源系に含まれるクロック電流がEMIの主原因と推定される

これは、以下の理由によります。

- 電源系には、クロック系を含むLSI内部のほぼすべての素子のスイッチング動作に伴う電流が存在し、プリント基板の電源分配回路に流れ込んでいると推定される。

- LSI電源ポートの等価回路を、LSI内部のクロック系回路のみの挙動で表現できることが判明した。

- プリント基板の電源分配回路は、高周波グラウンドを兼ねた平板構造が一般的である。このため、電源/グラウンド・プレーン間にはクロック成分を含む強い高周波電磁界が存在していると推定できる。

- 電源/グラウンド・プレーン間に信号配線が配置され、また信号ビアが電源プレーン間やグラウンド・プレーン間を横切っている。これらの信号配線の一部はコネ

クタを経由して外部ケーブルに接続されている。

これらのことから、筆者らは「LSI電源端子およびLSI内部の適切な回路ブロック単位の電源デカップリングを強化することにより、デジタル機器のEMI規格適合化問題を解決できる」と結論づけました。

### ◆ 磁界プローブによるLSIのEMI評価法が国際標準に

以上のような結論を導く過程で、筆者らはデカップリング性能の評価に必要なLSI端子の電源電流を測定するための磁界プローブを開発しました<sup>5), 6)</sup>。機器設計者がこの磁界プローブを使用して電源電流が大きい箇所を探し出してEMI対策を施すというのが、当初考えていた応用法です。しかしこの方法だと、ボードを試作しないと対策できないという問題があります。最近は機器の開発期間が短縮されており、試作を行わない例が増えているので、これでは困ります。

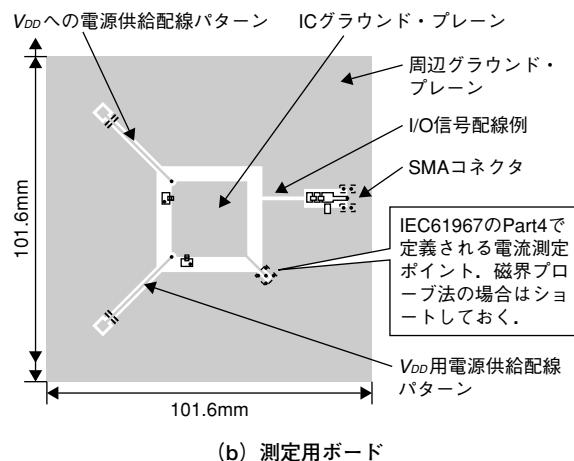

このような理由もあって、半導体事業グループの技術者といっしょに検討していたところ、この磁界プローブを使用してLSI単体で電源電流を測定すれば、LSIが機器に搭載されたときのEMI特性をかなり正確に推定できることが判明しました(図1)。上述のようにEMI問題はクロック成分の電磁波が主要因であり、LSI単体で電源電流を評価する際にはクロック信号を与えるだけによく、わざわざLSIが機器に搭載されたときの動作状態を模擬する必要はなかったのです。これならば、比較的簡単に評価できます。

EMC問題で苦労しているのは、LSI設計者よりも機器設計者のほうが多いと思います。機器設計者の立場からは、できるだけ多くのLSIメーカーがLSIのEMI特性の情報を開示してくれることが望ましいわけです。そこで筆

〔図1〕

磁界プローブ法

(MP Method)

磁界プローブを使用し、LSI単体の電源電流を測定するだけで、LSIが機器に搭載されたときのEMI特性を推定できる。

(a) 測定のようす

(b) 測定用ボード