### 期待値の比較 筆8回

安岡貴志

HDL で回路を記述できるようになったばかりで、これからテ ストベンチを書こうとしてる方を対象とした連載の第8回であ る. 前回(本誌 2008年7月号, pp.113-121の第7回)ま ででテストベンチに必要な文法の解説は、ほとんど終了した. 今回は第5回(本誌 2008年3月号, pp.107-115)でも触れ た期待値の比較に関して、より作業効率の良い自動化の方法を 解説する. (筆者)

# 1. 期待値の比較を自動化する

## ■ Verilog HDL・VHDL共通

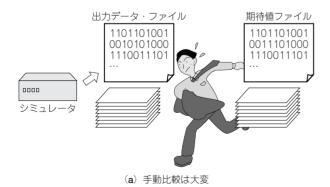

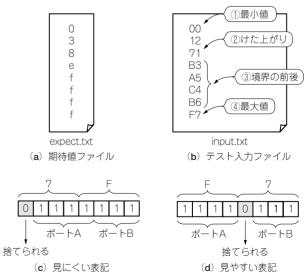

本連載の第5回では、期待値ファイルとシミュレーショ ンの結果ファイルを、diffコマンドなどで比較する方法を 紹介しました。しかし、テスト・パターン数が増えてくる と、すべてのパターンを手動で期待値チェックすることも 非常に煩わしくなります。また、人手が入ることでケアレ ス・ミスを生みやすくなります(図1).

Verilog HDLや VHDLでは、期待値ファイルさえあれ ば、テストベンチの中で比較することができます。ここで は、期待値の比較を自動化する方法を説明します.

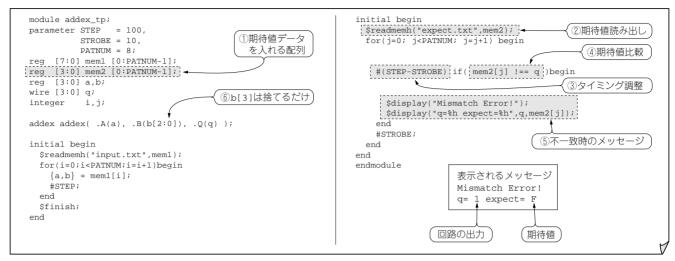

図2は、クリップ機能付きの加算回路です。この回路は 入力A, Bの加算結果をQに出力します。ただし、加算し た結果が16以上になった場合には、15を出力します。こ の回路の名前はaddex とします.

最初にこの回路を検証するテストベンチについて解説し ます、なお、今回のテストベンチでは期待値不一致のメッ セージを標準出力に出しています。ツール側でログ・ファ イルを出力する場合はこのままで構いませんが、そうでな い場合には標準出力ではなくファイルにメッセージを残す ようにしてください(連載第5回を参照).

# Verilog HDL

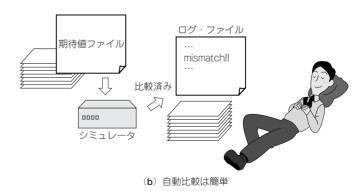

リスト1は、自動比較機能付きのテストベンチです。 リスト1の①は、期待値ファイルを読み出すための配列

図1 出力結果の比較

Keyword

シミュレーション・モデル, RAM モデル, include 文, package 宣言, 階層化, ModelSim, ライブラリ

#### リスト1 自動比較機能付きテストベンチ(Verilog HDL)

111

を宣言しています。出力 q は 4 ビットの信号なので、配列 のビット幅は4ビットです。期待値データの数は、テスト 入力のデータ数と同じでPATNUM (=8)としているので、配 列の番地の数は8個(0番地~7番地)です。

リスト1の②は、期待値ファイル expect.txt を配列 mem2 に読み出しています.

リスト1の③は、期待値比較するタイミングを調整して います. 入力信号は、0, 100, 200, ···, 700ns (#1=1ns のとき)で切り替わるようになっていますが、期待値比較 は90, 190, 290, …, 790ns (#1=1nsのとき) で行うよう に調整されています。

リスト1の④は出力信号 qと期待値を比較しています. ここで注意すべきことは、比較が!=ではなく、!==だとい うことです (p.129のコラム「等号演算子」を参照).

リスト1の⑤は、出力信号qと期待値が一致しなかった 場合にメッセージを出力します.「Mismatch Error!」の文 字とともに、現在のgの値とそれに対する期待値を表示し

図2 クリップ機能付き加算回路 addex の回路構造を示す.

ます、2行に分けているのは、単純に見やすさのためです。 1行で書いてしまっても問題ありません.

リスト1の⑥のように、b[3]は捨てられています。テス ト入力ファイル input.txt には、図3(b) のように、1行2文 字でテスト入力が書かれています。この2文字の区切り方 として、 $\mathbf{図3(c)}$  のようにポートA、Bに与えるデータを詰 めて書いてしまうと、それぞれに与えられるデータが何か、 人の目でファイルを見たときに、見にくくなってしまいま す. そこで図3(d)のように、ポートBに与えるデータを 4ビットで表記し、実際に与えるときに1ビット切り捨て ています.

図3 期待値ファイルとテスト入力ファイル テスト入力ファイルは、見やすい記述を心がける.