## プログラマブル・デバイス・レビュー

## ispPACによる アナログ回路の作成

川越靖

ディジタル回路のプログラマブル・デバイス (FPGA/PLD) は、さまざまな種類が発売されており、広く普及している。しかし、アナログ回路のプログラマブル・デバイスは、種類も少なく、まだあまり普及していない。本稿では、アナログ回路のプログラマブル・デバイスのうち、米国 Lattice Semiconductor 社のispPACシリーズを取り上げる。評価キットを使用して回路を試作し、実際に動作させた。 (編集部)

## はじめに

FPGA/CPLD は、現在ではハードウェア設計にはなくてはならない存在になっています。とくに、ISP (in system programming) 機能を備えたCPLD は、ディジタルIC の置き換えとして、実験試作から製品への採用まで、幅広く活躍しています。標準ロジックIC (74シリーズ、4000シリーズ)

の製造中止や廃品種が相次ぐなか、ソフトウェア的に対応できる CPLD は必須とならざるをえない状況です。

対照的に、アナログ回路については、それぞれの機能を1チップ化したスペシャル・ファンクションICが活躍しています。アナログ回路の場合、論理的なON/OFFだけではなく、温度特性、ノイズなど複雑な要素が数多く関係してきます。このため、できる限り簡単に使えるようにと、IC 化されていく傾向があるのです。しかし、特性がチューニングされているぶん、たくさん売れる分野向け(たとえば携帯電話)の製品はあるけれど、ちょっと機能が違うだけで別の用途では使えないとか、あるロットを出し終えてしまうと、すぐにモデル・チェンジといった状況で、カタログにあっても実際には入手できないといったようなこともしばしばです。

このような状況で、だれでも考えつくのが、アナログ回路

[図1] Lattice Semiconductor 社のホームページ

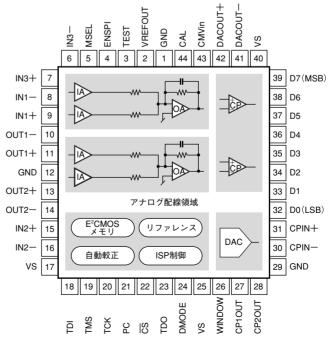

〔図2〕ブロック図

〔表1〕DC 特性

| 記号                                      | パラメータ         | 条 件                                           | min   | typ       | max        | 単位        |

|-----------------------------------------|---------------|-----------------------------------------------|-------|-----------|------------|-----------|

| PACblock アナロ                            | グ出力           |                                               |       |           |            |           |

| V <sub>IN ±</sub>                       | 入力電圧範囲        | <i>V<sub>IN+</sub>およびV<sub>IN-</sub></i>      | 1     |           | 4          | V         |

| $V_{\scriptscriptstyle IN\text{-}DIFF}$ | 差動入力電圧変動      | $2 V_{IN+}-V_{IN-} $                          | 6     |           |            | $V_{P-P}$ |

| $V_{DS}$                                | 差動オフセット電圧     | G=10<br>G=1                                   |       | 20<br>0.2 | 100<br>1.0 | μV<br>mV  |

| $\Delta V_{os} / \Delta T$              | 差動オフセット電圧ドリフト | - 40 ~ +85 °C                                 |       | 50        |            | μV/°C     |

| $R_{\scriptscriptstyle IN}$             | 入力抵抗          |                                               |       | 109       |            | Ω         |

| $C_{\scriptscriptstyle IN}$             | 入力容量          |                                               |       | 2         |            | pF        |

| $I_{\scriptscriptstyle B}$              | 入力バイアス電流      | DC                                            |       | 3         |            | pA        |

| $e_{\scriptscriptstyle N}$              | 入力電圧ノイズ密度     | 10kHz, G=10                                   |       | 38        |            | nv/√Hz    |

| PACblock アナロ                            | グ出力           |                                               |       |           |            |           |

| V <sub>OUT ±</sub>                      | 出力電圧範囲        | V <sub>OUT +</sub> およびV <sub>OUT</sub> -      | 0.1   |           | 4.9        | V         |

| V <sub>OUT - OFF</sub>                  | 差動出力電圧変動      | 2  V <sub>OUT +</sub> - V <sub>OUT -</sub>    | 9.6   |           |            | $V_{P-P}$ |

| I <sub>OUT ±</sub>                      | 出力電流          | ソース/シンク                                       | 10    |           |            | mA        |

| $V_{\scriptscriptstyle CM}$             | 同相出力電圧        | $(V_{OUT} + V_{OUT} -)/2 : V_{IN} + V_{IN} -$ | 2.475 | 2.500     | 2.525      | V         |

| PACblock 静特性                            |               |                                               | ,     |           |            |           |

| G                                       | プログラマブル・ゲイン範囲 | 各PACblock                                     | 0     |           | 26         | dB        |

|                                         | ゲイン・エラー       | R <sub>ι</sub> =300 Ω差動出力                     |       |           | 4.0        | %         |

|                                         | ゲイン・マッチング     | 同一PACblock の2入力間                              |       |           | 3.0        | %         |

| $\Delta$ G/ $\Delta$ T                  | ゲイン・ドリフト      | - 40 ~ + 85 °C                                |       | 20        |            | ppm/°C    |

| PSR                                     | 電源除去率         | 1kHz (差動)<br>1kHz (シングルエンド)                   |       | 80<br>77  |            | dB<br>dB  |

$V_{N+}$   $V_{N-}$   $V_{N-}$

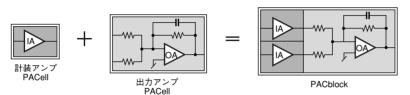

「図3] PACblock とPACell の関係

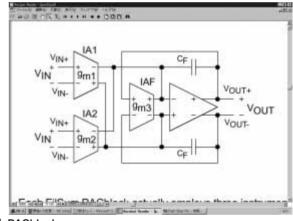

〔図4〕PACell

のCPLDです。「OPアンプとアナログ・スイッチを組み合わせれば簡単なんじゃないの」と思われる方もいるかもしれません。ただ実際の応用として考えると、対象とする用途により、オフセット、スルーレート、抵抗、コンデンサ、精度などの要求もばらばらで、やっぱりアナログでのCPLDは構成不可能なのだろうかと、思ったものでした。

そんな折、CPLDメーカの米国Lattice Semiconductor社からアナログCPLD(?)ispPACが登場してきました(図1).

## ●ispPAC の内部構成

ispPAC は、In System Programmable, Programmable Analog Circuit の略で、Lattice Semiconductor 社から発売された、アナログ機能のPLDです。

アナログというと、まずはOPアンプが思いつきます. ispPAC はブロック化されたOPアンプを1チップ内に実装し、その間をプログラマブルに接続できる、と考えればいいと思います。図2および表1にispPAC20の基本構成とDC特性を示します.

ispPAC の中核を成すのがPACblock と呼ばれるOP アンプの代わりをする回路ブロックです。このPACblock は、図**3**のように、PACell と呼ばれるトランス・コンダクタ・アン

〔図5〕PACblock

プから構成されています。PACell (図4) は入力差電圧に比例した電流が出力されるものです。PACell の増幅率 (コンダクタンス: $g_m$ ) は $2\mu\sim20\mu$  A/V で10 段階でプログラマブルに切り替えられるようになっています。この引き込み電流を変化させることで,等価的にプログラマブル・ゲイン・アンプとしてのゲインを決めることができます。また,入力インピーダンスは,1,000M  $\Omega$ 以上と非常に高い値となっていますので,簡易的には,差動入力のOP アンプと同等と考えてさしつかえありません。

PACblockでは、このようなPACellが図5のように接続されています。二つの入力値の値をゲイン・アンプで受け、