# 連載 (第8回) 「論理合成」は「魔法の道具」にあらず

## フルカスタム化の方向へ向かうセミカスタムLSI

論理合成技術の将来

藤田昌宏

今回は、カスタム・セルを利用したセル・ベースICの設計手法について紹介する。現在のASIC用論理合成ツールは、半導体メーカが用意したマクロ・セルを組み合わせて回路を構成する。しかし、もう一段の性能向上や消費電力の低減を実現するためには、各設計に最適化されたカスタム・セルを導入する必要がある。これは、マイクロプロセッサなど、フルカスタムLSIの設計でよく用いられている手法である。今後は、セミカスタムLSIの設計にフルカスタムLSIの手法が取り入れられると筆者は見ている。(編集部)

今回は、本連載の最終回として、論理合成研究の現状からみて、ここ数年以内に実用化されそうな技術動向の中から、特にASIC(セル・ベースIC)のフルカスタム化の問題について解説したいと思います。

#### ●フルカスタム手法の導入に向かうASIC

さて前回、ASICはFPGAに取って代わられるかもしれないと述べましたが、ASICのほうにも改善すべき点、あるいは改善できる点は多々あります。そのもっとも重要なものの一つが「性能改善」です。もし、FPGAがASICに取って代わるのなら、ASICのようなセミカスタムLSIでフルカスタムLSIなみの性能が出るようにして、フルカスタム設計に取って代わろうという考えかたです。これは、ひと言で言えば、回路の高速化、あるいは低消費電力化を目指すということです。

セミカスタムLSIとして現在もっとも広く使われているセル・ベースICの場合、セル・ライブラリに登録されているセルのみを利用して論理回路を作成し、自動配置配線を行うことで、最終的なマスク・パターンを作成しています。

このセル・ライブラリには、AND、OR、NAND、NORなどの基本ゲート以外にも、AND-OR-INVERTERやEXCLUSIVE-ORなどの複雑な論理、さらには、加算器、ALU、乗算器などの算術演算回路などが登録されています(もちろん、フリップフロップやレジスタなどの順序回路素子も多数あるが、ここでの議論には直接関係しないため、省略する)。また、それぞれの機能について、1種類ではなく、大きさの異なるトランジスタを用いた複数種類のセルが用意されています。これらをうまく組み合わせることで、回路面積と遅延時間、消費電力などのトレードオフを利用して、回路を最適化できるようになっています

算術演算回路の場合,使いたい機能のセルが登録されていれば,それをそのまま使えばよいわけですが,制御回路や,やや通常と異なる算術演算を行う場合などには,必ずしも実現したい機能そのものズバリのセルがない場合が多いと考えられます.そのような場合,使いたいセルを自由に設計できるフルカスタムLSIに性能面で劣ることになります.

そこで、それぞれの設計に対して、専用のセルを使えるようにすれば、セミカスタムLSIでもかなりフルカスタムLSIに近くなり、LSIの性能向上を図れると考えられます。ここでは、設計に応じてセルを自動的にカスタムメイドする技術について、説明したいと思います。なお、これはEDAベンダから近々ツールが登場するような、ごく近い将来の話です。

#### ●セミカスタムLSI 設計の流れ

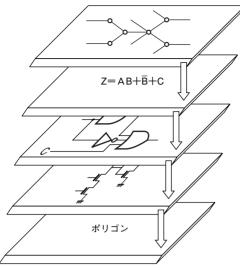

まず、セミカスタムLSI設計の流れを復習しておきましょう。図1を見てください。

最初に、データ・フロー・グラフや状態遷移図で表現

### |論理合成|は「魔法の道具|にあらず

〔図1〕LSI設計の流れ

データ・フロー・グラフや状態遷移図で表現されたRTL(レジスタ転送レ ベル)の記述から論理式が生成され、それを簡単化し、テクノロジ・マッ ピングによって論理回路に変換される。さらに各ゲートは対応するトラン ジスタ・レベルの回路になり、最終的にマスク・パターン(ポリゴンの集 まり)に変換される.

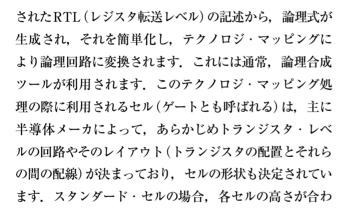

〔図2〕カスタムセルの自動生成を利用した設計手法

セミカスタムLSIでは、簡単化、テクノロジ・マッピングにより、論理式 からセル・ライブラリに登録されたセルのみからなる論理回路に変換され る. これに対して、個々の論理式の集まりに応じて、カスタム・セルを 自動生成すると、設計ごとに回路を最適化でき、性能向上を期待できる。

せられています.

セルの高さが合わせられているため、セルの配置やセ ル間の配線は、セル領域と配線領域を明確に区別して行 うようにレイアウト・ツールが設計されています。したが って、かりにセル・ライブラリに入っていなかったもので も、セルの高さを合わせておけば、通常のセル・ベース IC用のレイアウト・ツールで配置配線を行えるはずです。

そこで、図2に示すように、RTL 記述から生成された 論理式に対して、性能がもっとも向上するようなカスタ

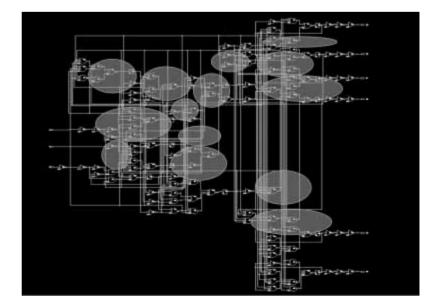

#### [図3]

#### 大規模回路からカスタム・セルを生成するべき箇 所を抽出

回路全体が与えられ、タイミング解析など、論理回路 に対する解析の結果から、性能向上を図るべき回路部 分を決定する。 それらの回路部分の中から、 適当な手 法によってカスタム・セルとして適当な大きさの回路ブ ロックを抽出する.