# 第4章

## シグナル・インテグリティ・ クライシスの「傾向と対策」

伝送線路設計の基本原則を一つ一つ

確実に適用してトラブルを回避

中川政雄

ここでは高速デジタル・ボードにおける伝送線路設計の問題について解説する。伝送線路シミュレータやIBISモデルはかなり利用されるようになってきた。しかし、基本事項を理解していないために生じるトラブルはけっこう多い。ここでは、伝送線路設計の基本事項、伝送線路シミュレータの活用法、設計現場で頻繁に発生しているトラブルの具体例、およびその対処法などを紹介する。

(編集部)

プリント基板設計の打ち合わせの席でのことです。回路設計を担当するAさんは、「ここは高速なので、伝送線路シミュレーションを実施してください」と、回路図中のASICとSDRAMのインターフェース部分を指しました。「わかりました」と基板設計担当者が答え、「ではこのバス・クロックは何MHzですか」と聞き返しました。Aさんは「うーん...」と考え込んでしまったあげく、「調べて、後からご連絡します」ということになりました。自分が設計した回路図の信号速度がわからない、こんなケースはAさんに限った話ではありません。

### ●信号周波数が変化すれば、適切な配線構造が変わる

なぜAさんのようなことが起こるのでしょうか。このよう

なケースの担当者は、「LSIメーカーから出された仕様書に記述された参考回路図を丸写ししている」と言われる方がほとんどです。

参考回路図には、ICとICの接続情報は書かれていますが、信号周波数がいくつかといった情報は書かれていません。しかし、信号周波数によってはプリント基板設計の方法、つまりは伝送線路の設計手法を変えていかなくてはなりません。回路設計者が回路の情報を把握していないようでは、プリント基板の設計品質の向上はありえないのです。

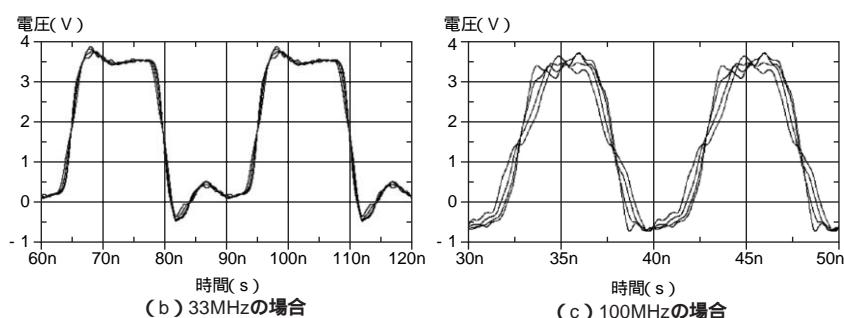

図1は、一つのICから四つのICを駆動する回路をシミュレーションした例です。33MHzでは問題がないように見えますが、100MHzでは1.5V付近で誤動作につながりかねない段差が生じています。

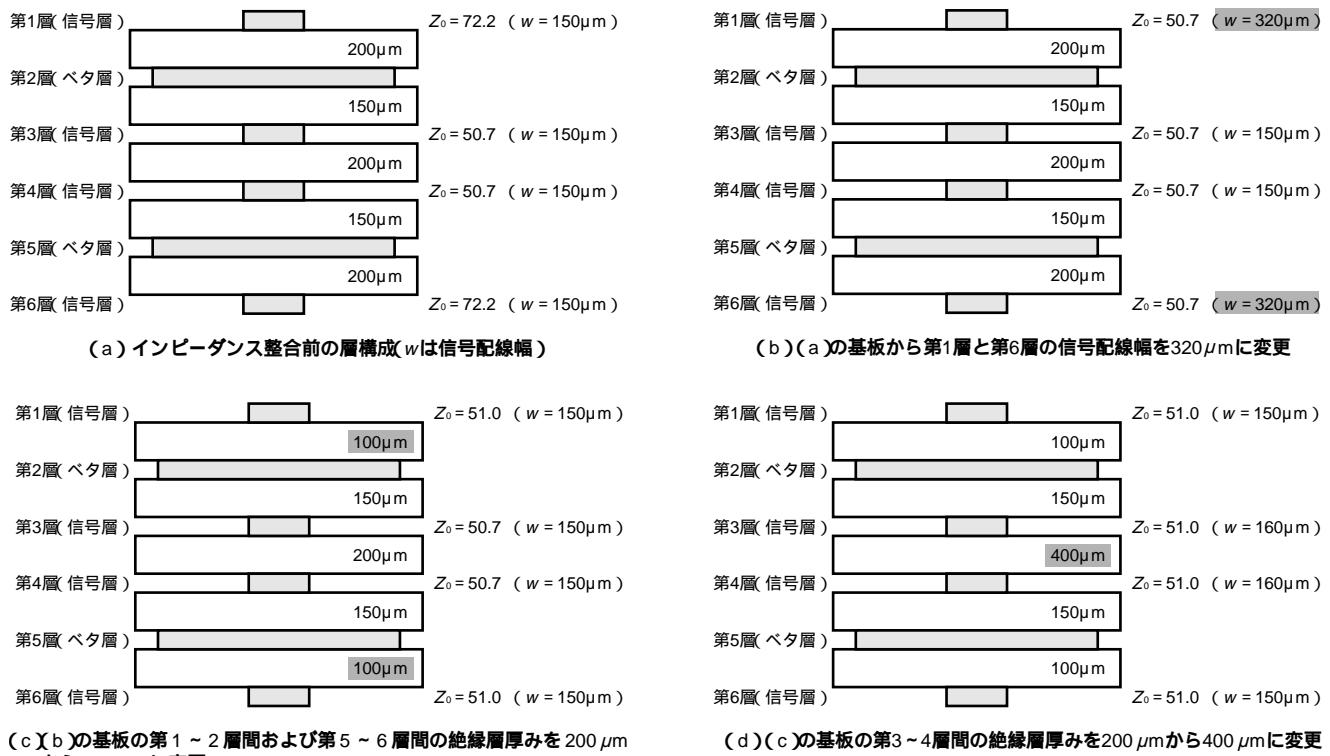

同じ回路を図2のように分岐型のトポロジに変更してみましょう。問題のない波形が出てきました。一般的には、全体の配線長を短くできるケースが多いため、図1のよう

[図1]

### ひと書きトポロジとそのシミュレーション結果

ひと書きトポロジは、低速回路では良いが、高速回路に用いる「反射」の問題が顕在化し、無視できない波形の乱れが現れる。なお、(c)のシミュレーションでは、デバイスを高速用の品種に変更している。

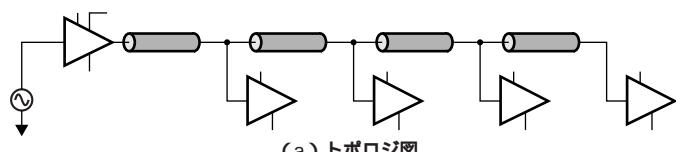

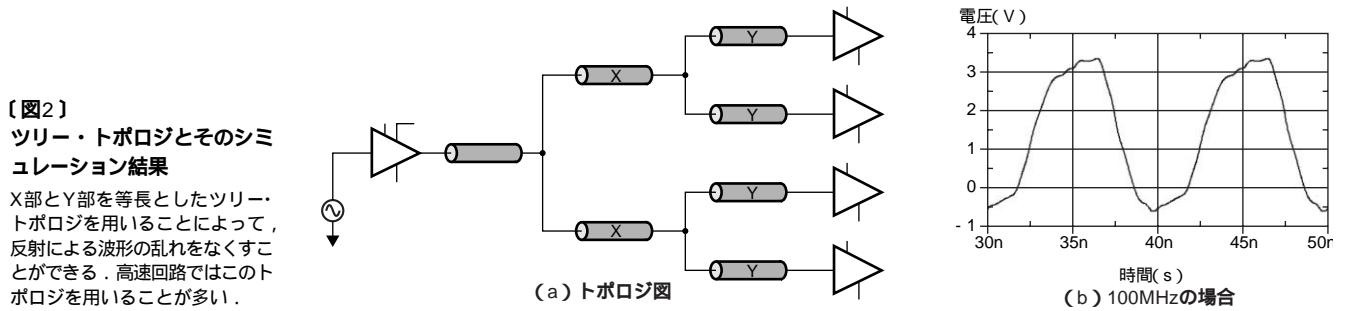

### 【図3】インピーダンス整合の例

各基板メーカーごとに標準として持っている層構成(例えば(a))を用いるだけでは、インピーダンス整合を達成できないケースが多い。(b)～(d)のような過程をたどりながら、満足のいく層構成を導き出す。

なひとつ書きの配線トポロジが多く用いられます。しかし、図1からわかるように、信号周波数によっては、これは適当な選択であるとはいえない。

このような形で設計を進めたものは、原因不明の誤動作に苦しめられ、ひたすら試作を繰り返すことになるでしょう。また、製品として完成できたとしても、初期に想定していた性能を100%引き出せなかったり、十分なマージンを確保することができなかつたため、製品発売後のクレームに至ることさえあります。

特に最近では、民生機器(コンシューマ機器)の分野で

も、DDR(double data rate)SDRAMの利用が目立ってきました。速度の早いDDR SDRAMは、セットアップ/ホールド時間確保の観点から、厳密な伝送線路設計が必要となります。

筆者がLSI設計者と話をするときにもよく話題となるのですが、LSI設計者の立場でもDDR SDRAMの利用は難しいとのことです。どんなに優れたLSIを使っても、いくら回路図が書けても、それを使いこなす(ボード上に展開する)能力を身につけていなければ「物づくり」としては破たんします。それを防ぐには、これから述べていくような伝