#### シノプシスとメンターグラフィックスにおける Design Reuseの取り組み

- SoC設計の成功を導 《OpenMore / Reuse Methodology Manual 2

日本シノプシス株式会社 技術本部 SVPグループ グループマネージャ \_\_\_\_\_ 岡野 郁美 メンター・グラフィックス・ジャパン株式会社 IP & コンサルティング技術部 IP技術サポート担当 枝 均

#### Agenda

- Synopsys とMentor Graphics のIP Reuseに対するパートナーシップの あゆみ

- MOREからOpenMOREへ

- OpenMOREの紹介

- Synopsys での OpenMORE に対する活動

- Mentor Graphics での OpenMORE に対する活動

- OpenMORE Assessment Program

- RMM2 Guideline Example

- Check Listの使用時のPoint

- OpenMORE を取り巻 く技術

- What's Next?

#### 3年に渡るDesign Reuse パートナーシップ

- DAC 1997 Anaheim

- ・ Design Reuse パートナーシップの発表

- DAC 1998 San Francisco

- ・ Reuse Methodology Manual の出版 (RMM)

- DAC 1999 New Orleans

- Reuse Methodology Manual 第 2版出版

- ・ OpenMORE の発表

- IP99 Edinburgh

- OpenMORE assessment program リリース

- ・ www.openmore.comでのアクセス

#### Reuse に対する第一ステップ (MORE)

- IP コアに対するreusability の評価ツール

- Synopsys Web site上で提供, December 1998

- 1,000 を越えるユーザーからのアクセス

- MORE を基準とした評価

- 10 ページの評価シート

- RMMからの130 のルール及びガイドライン (1/3 conditional)

#### OpenMORE™ 評価プログラム

- 新しい Mentor/Synopsys によるOpen Measure of Reuse Excellence 評価プログラム (OpenMORE)

- Mentor Graphics とSynopsys の協力関係

- オリジナルのSynopsys MORE 評価プログラムを拡張

- SoC に必要とされる IP 再利用性に注目

- SoC設計のためのIPの再利用性を評価する手 段の提供

#### OpenMORE ...

- ソフト及びハードPの設計・検証のための 新しい評価項目を追加

- Reuse Methodology Manual 第 2版より

- VSIA からの主な項目を取り入れ

- industry group からのサポート VSIA, VCX, RAPID, Design & Reuse

- 以下のサイトによりアクセス可能

www.openmore.com

#### www.openmore.com

| ţ          | Welcome to OpenMORE.com |                 |  |

|------------|-------------------------|-----------------|--|

| home conta | About                   | News            |  |

|            | Download                | Events          |  |

|            | RMM2                    | Resources       |  |

|            | Synopsys                | Mentor Graphics |  |

in the industry are saying about OpenMORE.

# Open**MORE**

#### The Industry Reference for IP Measure of Reuse Excellence

Mentor Graphics and Synopsys have joined forces to help make IP reuse a reality. The reusability of IP cores is a critical factor in the speed and predictability of IP integration, and significantly affects the success of an entire System on a Chip (SoC) project. A key aspect of building the IP infrastructure is devising a method to evaluate and qualify IP for project use.

OpenMORE is a reference scoring program for assessing the reusability of hard and soft IP cores for SoC design. The assessment program includes the complete set of rules and guidelines from the original Synopsys MORE program, the recently released Reuse Methodology Manual (RMM) Second Edition, authored by Mentor Graphics and Synopsys, and key deliverables from the Virtual Socket Interface Alliance (VSIA) industry group.

OpenMORE provides the industry's premier methodology to simply and quickly evaluate the reusability of IP cores for SoC design.

#### MOREを拡張したOpenMORE

- OpenMORE(Hard IP)

- 90 guidelines

- System level design issues

- RTL coding guidelines

- Developing hard macros

- Verifying hard macros

- System-level verification

- RMM deliverables

- VISA deliverables, document 2.0

- OpenMORE(Soft IP)

- Design Guidelines

- 123 guidelines

- Verification Guidelines

- 21 guidelinesnew guidelines for:

- Prototyping

- Formal verification

- Gate level simulation

- specialized hardware for System Verification

- Deliverable Guidelines

- 13 guidelines

#### IP User とIP Supplier への OpenMOREの利点

- IP supplierは市場にリリースする前の評価 として使用可能

- IP supplierはOpenMOREの結果を競合との 差別化として利用できる

- IP customers はIPを選択する際の手段の 一つとして利用できる

# How Synopsys Uses OpenMORE

#### SYNOPSYS°

#### How Synopsys uses OpenMORE

デザインコンサルティング

設計環境コンサルティング

**IP Catalyst**

SNPS/MENTパートナーシップ

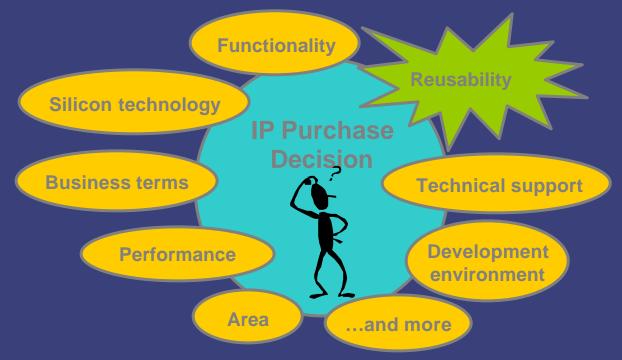

#### OpenMORE -IP Userが市販のIPを 選択する際の手段の一つ

再利用性はIP integration のスピードと事前の 見積もりに対する最も重要な要素の一つ

#### SYNOPSYS°

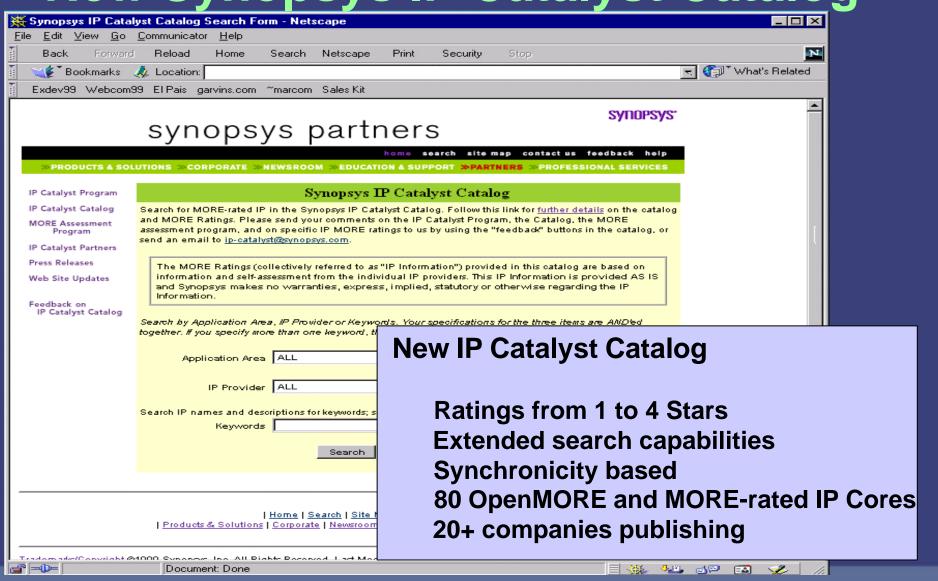

#### Synopsys IP Catalyst Catalogから Reuse-Ready IPを検索

- Reuseに対して評価された市販のIPを Synopsys IP Catalyst Catalogへ記載

- OpenMORE とMORE-rated IP を 20+ IP ベンダ

- ーから検索可能

www.synopsys.com/ipcatalyst

#### <u>Synopsys</u>°

#### SYNOPSYS® | IP Catalyst

#### New Synopsys IP Catalyst Catalog

SYNOPSYS® | IP Catalyst

Catalog

#### OpenMORE スコアから発表される

**OpenMORE** Rating

1. IP Vendor completes IP self-assessment

3. Synopsys assigns **OpenMORE** Rating

**Other** IP

**OpenMORE** assessment program

**IP Vendor** confidential

EDA TechnoFair 2000

## How Mentor Graphics Uses OpenMORE

#### ☐ How Mentor Graphics uses OpenMORE

(Intellectual Property)

Inventra IP DataBook

デザイン サービス

設計コンサルティング

#### **Uses OpenMORE...**

OpenMORE Assessment Program RMM2 Guideline Example Check List 使用時のPoint OpenMOREを取り巻 (技術 What's Next?

#### RMM2

#### **OpenMORE**

- System-level Design Issue

- RTL Coding Guideline

- Macro Synthesis Guidelines

- ...

SYNOPSYS°

#### OpenMORE アセスメントプログラム

- Soft IP アセスメント

- Hard IP アセスメント

2種類の測定ガイドがある。

**Hard IP Assessment**

#### □ Hard/Soft IP アセスメントの主な項目

- マクロデザイン ガイドライン 再利用を目的としたIPの設計開発について

- ベリフィケーション ガイドライン 再利用が可能なテストベンチやテストにおける 問題点について

- デリバラブル ガイドライン 関係するファイルのパッケージングとデリバリーに ついて

□ Soft IP アセスメント

total 730点

- マクロデザイン ガイドライン

- System-level Design Issue

- RTL Coding Guideline

- Macro Synthesis Guidelines

- ベリフィケーション ガイドライン

- Macro Verification

- System-Level Verification

- デリバラブル ガイドライン

- RMM Deliverable

<u>542</u> 点 88 346 配点が大きい

108

74 26 48

114 114

#### SYNOPSYS°

□ Hard IP アセスメント

total 586点

| ■ マクロデザイン ガイドラ・ | 1ン |

|-----------------|----|

|-----------------|----|

- System-level Design Issue

- RTL Coding Guideline

- Developing Hard Macros

#### ■ ベリフィケーション ガイドライン

- Verifying Hard Macros

- System-Level Verification

#### ■ デリバラブル ガイドライン

- RMM Deliverable

- VSIA Deliverable

#### 174 点

- 22

- 20

- 132

- <u>44</u>

- 30

- 14

**368**

58

310

#### SYNOPSYS°

#### □ Soft IP アセスメントの一部

| Max | Score |

|-----|-------|

|     |       |

| 1       | Macro Design Guidelines                                         | 542 |

|---------|-----------------------------------------------------------------|-----|

|         | :                                                               |     |

| 5       | RTL Coding Guidelines                                           | 346 |

| 5.2     | Basic Coding Practics                                           | 190 |

| 5.2.1   | General Naming Coventions                                       | 52  |

| 5.2.1.1 | Documented naming conventions used :                            |     |

| 5.5     | Coding for Synthesis                                            | 50  |

| 5.5.1   | Infer Register                                                  | 2   |

|         | :                                                               |     |

| 5.5.8   | Case Statements versus if-then-else Statements                  | 2   |

| 5.5.8.1 | Case statements used rather than an if-then-else                |     |

|         | statement wherever appropriate. :                               | 2   |

| 5.6     | Partitioning for Synthesis                                      | 22  |

| 5.6.1   | Register All Outputs                                            | 2   |

| 5.6.1.1 | For each block of a hierarchical design, all output             | 2   |

| 5.6.2   | Related Combinational Logic in a Single Module                  | 2   |

| 5.6.2.1 | Related combinational logic placed together in the same module. | 2   |

|         | :                                                               |     |

紹介(その1)

紹介(その2)

#### □ マクロデザイン ガイドラインの紹介 (その 1)

RTL Coding Guideline5.5 Coding for Synthesis

5.5.8 Case Statements versus if-then-else Statements

"Case"文と"If-then-else"文の違いは?

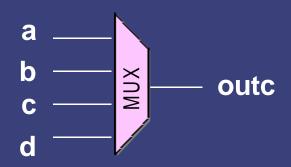

#### ●if文とase文の違い

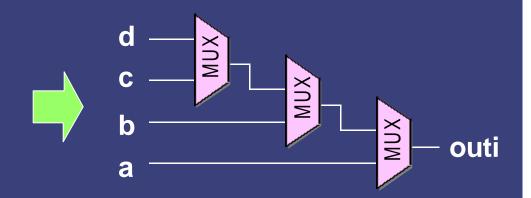

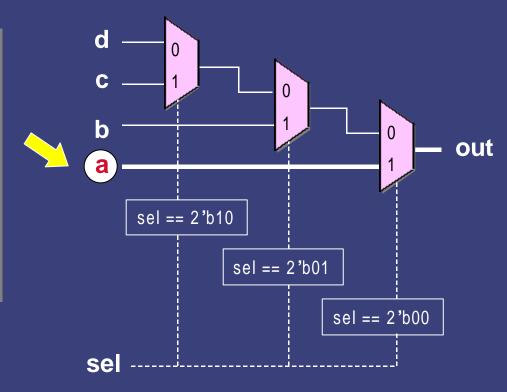

#### ◆ プライオリティ化 (if文)

#### ◆ パラレル化 (case文)

```

case (sel)

2'b00 : outc = a;

2'b01 : outc = b;

2'b10 : outc = c;

default : outc = d;

endcase;

```

#### ● if文からプライリティ·エンコーダーが合成される

#### aからoutまでの遅延時間が一番小さい

```

always @(sel or a or b or c or d)

begin

if (sel == 2'b00)

Out = a;

else if (sel == 2'b01)

out = b;

else if (sel == 2'b10)

out = c;

else

out = d;

end

```

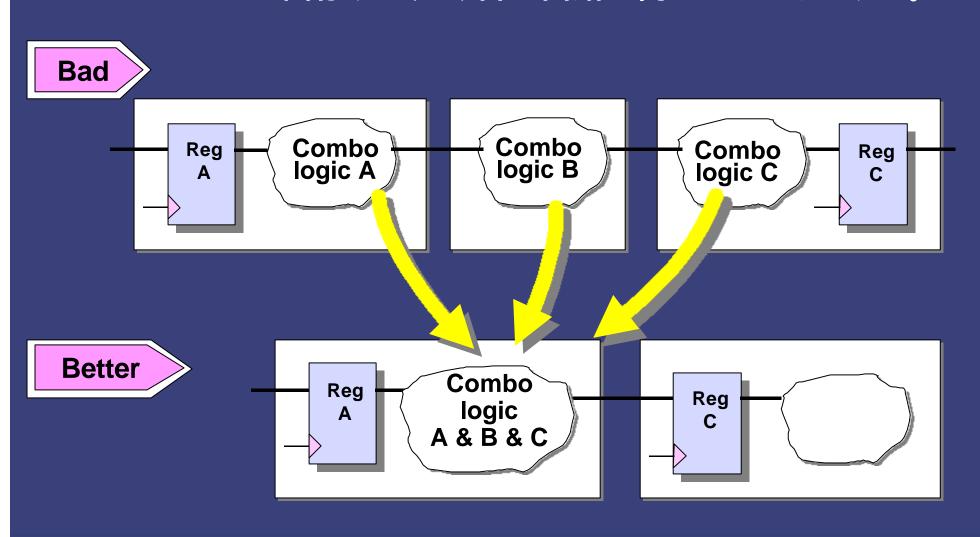

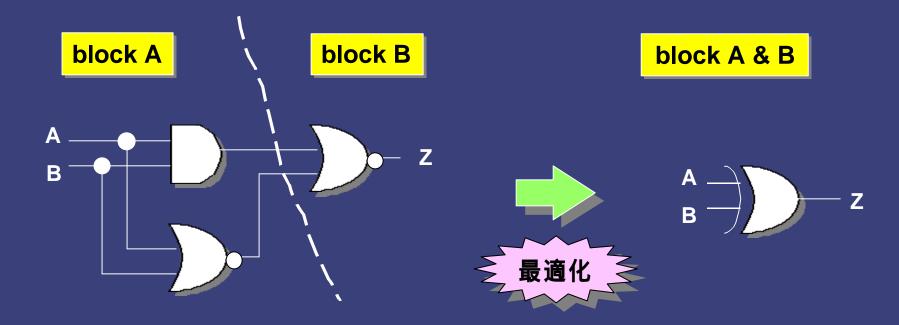

#### □ マクロデザイン ガイドラインの紹介 (その2)

RMM2より

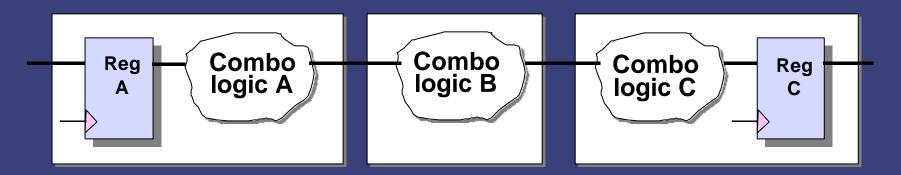

RTL Coding Guideline5.6 Partitioning for Synthesis

5.6.2.1 Related combinational logic placed together in same module

ブロック分割の問題点は?

#### SYNOPSYS°

■ ポイント1:関係する組み合せ回路は同一ブロックにする。

#### ■ ポイント1 (補足)

- ブロックのインターフェス部は冗長な論理が残る。

- 合成ツールはブロックを跨いでの最適化はしない。 倫理合成時に特定の制約を与えない限り)

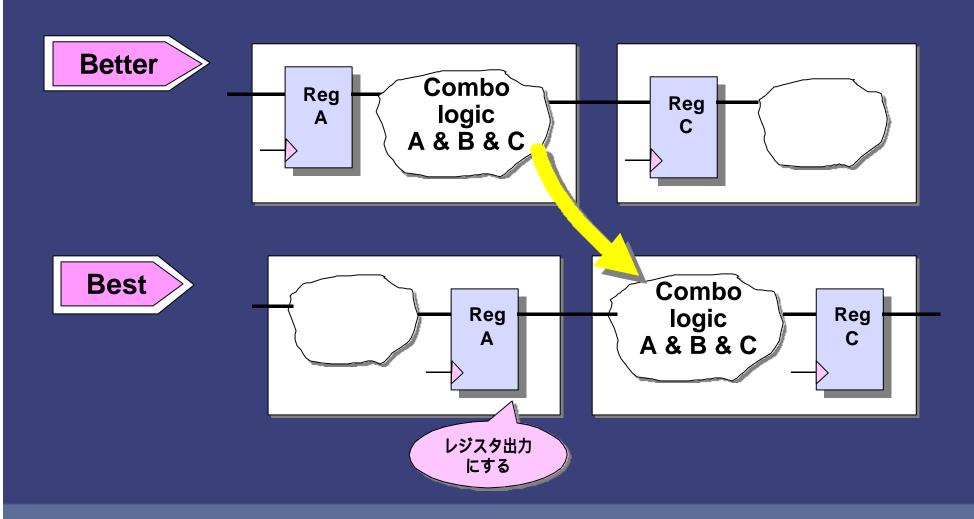

■ ポイント2:ブロックの出力は、レジスタ出力にする。

■ ポイント2 (補足)

- ブロックの各出力遅延値がほぼ一定になり、見積もりが容易。

- ●合成スクリプトの共通化と簡素化。

#### チェックリスト使用時のポイント

- ■背景を知る

- 盲目的使用は危険

- 優先順位をつける

- 重要度は状況により変わる

- IP作成者と使用者との間のコミュニケーション手段

### OpenMOREを取り巻く技術

- Packaging for Reuse

- User Interface

- Un-packaging flow

- IP Integration

- Timing Closure

- Manufacturing Test

- System-Level Verification

#### What's Next?

- Promote OpenMORE acceptance and tools to generate OpenMORE/VSIA compliant IPs

- Continue work with Industry study groups VSIA, VCX, D&R, Rapid)

- OpenMORE Update Release (Hard IP section 1.0 )

- Investigate future opportunities (Memory, On Chip Bus (OCB))

#### Access to OpenMORE

## www.openmore.com