# FPGAでシリアルATA コントローラを設計する

第 4 回 シリアルATAコアとシミュレーション

菅原 博英

前回までに設計したシリアルATAコントローラのコア(SATA\_CORE)のシミュレーションを行う。

(編集部)

## 1. コア全体シミュレーション

コードの解説を読むだけでは、SATAの動作を理解するのはなかなか難しいと思います。今回はRTL設計に伴うシミュレーション環境を設計します。

このうちのリンク層の確認を実行させます。まずPHYの初期化完了後、最初に送信されるRegD2Hを試してみます。最も簡単な制御FIS (Frame Information Structure)なので、リンク層のHOLD/HOLDAによるフロー制御は

発生しません.

#### ● テスト・コード

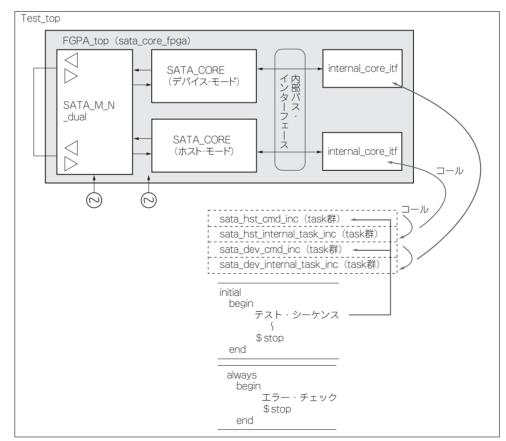

テスト全体のファイル構成をリスト1に, test\_top配下にある全体の概要を図1に示します. xxx\_cmd\_inc.vはテスト動作をなるべく抽象的に記述したタスク群です. これらが, xxx\_internal\_task\_inc.vを経由してinternal\_core\_itf.v内の内部バス動作を実行させます.

(1) xxx\_cmd\_inc.v

DEV\_INIT のタスクをリスト2に示します.

DEV\_INIT は、デバイス側の SATA\_CORE ヘレジス

凶1 test\_top配下の全体概要

#### リスト1 テスト全体の ファイル構成

```

\verilog\test\sata_core\test_top.v

・最上位干ジュール

:ポート定義ファイル

\verilog\test\sata core\sata core ports inc.v

+- \verilog\rtl\fpga_top\sata_core_fpga.v

・FPGA のトップ

:各サブモジュール

+-- \verilog\rtl\bhv test\internal core itf.v

+-- \verilog\rtl\sata_core\全部

+-- \verilog\core\bhv\SATA_PHY_dual bhv.v

+-- \verilog\core\bhv\DCM CLK bhv.v

+-- \verilog\core\bhv\RAM32bX64w bhv.v

\verilog\test\sata core\sata core clock inc.v

:クロック定義ファイル

\verilog\rt1/bhv test/sata task reg inc.v"

:パラメータ定義

:各ドライバ

\verilog\rt1/bhv_test/sata_hst_cmd_inc.v

\verilog\rt1/bhv_test/sata_dev_cmd_inc.v"

\verilog\rt1/bhv_test/sata_hst_internal_task_inc.v

+-- \verilog\rt1/bhv_test/sata_dev_internal_task_inc.v"

```

タ・アクセスを実行する DEV\_REG\_R と DEV\_REG\_W を 用います.最初に Status レジスタを確認します.PHY が Ready になるまでは 7Fh が読めるので,それを繰り返し, 80h が読めたら各レジスタを初期化します.最後に DEV\_REGDH を呼び出して RegD2H 送信を起動します.

#### (2) xxx internal task inc.v

$sata_dev_\sim .v$  内に  $DEV_REG_R$  のタスクがあります。 それをリスト3に示します.

上位からのアドレス (adr) を TRNS\_TFR の要求するアドレス (IOadr) に変換して、内部バス動作 (DEV\_REG\_R) を実行させています。完了後、internal\_core\_itf.vでリード値 (reg\_rd) の再代入を行います (dev\_reg\_rd).

### internal core itf.v

ITF\_REG\_R のソースを**リスト4**に示します.

#### リスト2 DEV\_INITタスク

```

task DEV INIT:

begin

DEV_REG_R(StatusReg)

while(dev_reg_rd==16'h007F) begin

while((dev reg rd==16'h007F)

|(dev_reg_rd==16'h0000)) begin

DEV_REG_R(StatusReg)

end

DEV_REG_W(FeatureReg

,16'h0000)

DEV_REG_W(ErrorReg

,16'h0000)

,16'h0050)

DEV_REG_W(StatusReg

DEV_REG_W(DevHeadReg

,16'h0000)

,16'h0012)

DEV_REG_W(CylHighReg

,16'h0034)

DEV_REG_W(CylLowReg

,16'h0056)

DEV_REG_W(SctNumReg

,16'h0078)

DEV REG W(SctCntReg

,16'h009A)

DEV_REG_W(CylHighReg

DEV_REG_W(CylLowReg

.16'h00BC)

DEV REG W(SctNumReg

,16'h00DE)

DEV REG W(SctCntReg

.16'h00F0)

DEV REGDH

end

endtask

```

アドレス (adr=DEV\_REG\_R では IOadr) を O\_CMD\_ xxx として出力し、アクセス待ち (I\_CMD\_NRDY) がない ことを確認します. ただし、DATA レジスタへのアクセ ス以外は I CMD NRDY は常にネゲートです.

出力信号の更新は、@(posedge CLK)でクロックに同期させつつ、少し遅延させて(#1)行います。一方の入力信号は、@(negedge CLK)や遅延(#1)などを用いて、安定した時点で確認します(#1だけの文はエラーになることがあるので、dummyへ代入)。ITF\_REG\_Rではリードした値を変数(reg\_rd)へ取り込みます。

最後に、アドレスなどを0に戻して終了です。O\_CMD\_ REとO\_CMD\_WE以外はそのままでもレジスタ・バス仕様上は大丈夫ですが、シミュレーション波形を見やすくするために0へ戻します。

#### ● リンク上位層確認

シミュレーションに必要なモジュールをコンパイルし、 波形ファイルを開いて  $20\mu s$  程度実行すると、最初の Reg D2H の送信が完了します.

#### リスト3 DEV\_REG\_R タスク

```

task DEV REG R

input

[6:0]

adr :

reg [6:0]

TOadr

begin

casex({adr[6:3]})

4'b0010:IOadr={3'b01_1,1'b0,adr[2:0]};//Normal

4'b1011:IOadr={3'b01_0,1'b0,adr[2:0]};//Read to Wonly

4'b1010:IOadr={3'b01_1,1'b0,adr[2:0]};//Read to Ronly

4'b0100:IOadr={3'b10_1,1'b1,adr[2:0]};//Contol

4'b1101:IOadr={3'b10_0,1'b1,adr[2:0]};//Read to Wonly

4'b1100:IOadr={3'b10_1,1'b1,adr[2:0]};//Read to Ronly

4'bx11x:IOadr={3'b11_0,

adr[3:0]};//Other Control

endcase

`FPGA_TOP.dev_sml.ITF_REG_R(IOadr);

dev_reg_rd =`FPGA_TOP.dev_sml.reg_rd

//-

end

endtask

```

Interface Oct. 2008