# 組み込みシステム 開発評価キット 活用通信

第1フ回▮オプション CPU カード Blackfin (ADSP-BF533) の設計

# i 1. E!Kit-BF533の設計

組み込みシステム開発評価キット (通称 BLANCA) のオプション CPU カードとして、DSP を搭載する CPU カード ElKit-BF533 を設計・開発しました。ここでは ElKit-BF533 について解説します。

#### ● Blackfin DSP とは

ElKit-BF533 には CPU として、DSP である Blackfin (Analog Devices 社製) を搭載しています。Blackfin は 16/32 ビット組み込みプロセッサです。オーディオ、ビデオ、通信データ情報を統合したマルチメディア処理に適しています。Intel 社と共同開発したマイクロ・シグナル・アーキテクチャ (MSA) をベースに、32 ビットの RISC ライクな命令セットと二つの 16 ビット積和演算 (MAC)、各種周辺機能を内蔵しています。詳細仕様やデータ・ブックなどは、同社の Web サイトから入手可能です。

## BLANCAローカル・バス バッファ バッファ タ・バス16ビット アドレス・バス 19ビット +3.3V +3.3V コア電圧 +1.8VSDRAM フラッシュROM Blackfin CPLD ADSP-BF533 (64Mパイト) (4Mパイト) JTAG

図1 E!Kit-BF533 ブロック図

#### ● E!Kit-BF533

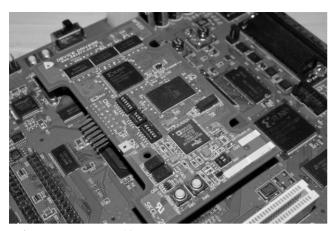

E!Kit-BF533 は 100mm × 60mm の大きさのボードに 600MHz で動作する Blackfin プロセッサ ADSP-BF533 と, 64M バイトの SDRAM, 4M バイトのフラッシュ ROM, BLANCA のオプション CPU カード用コネクタ, JTAG コネクタなどを搭載した, 学習・実験用途向け組み込みボードです. 写真1 のように, BLANCA などに実装して使用します.

E!Kit-BF533の主な仕様を**表1**に示します. ブート・ローダ としては、複数のCPU アーキテクチャに対応し、GPL (General Public License) のもとにリリースされている U-Boot を採用しています.

#### ●ボードの構成

図1に ElKit-BF533のブロック図を示します. ADSP-BF533のバスには SDRAM とフラッシュ ROM が接続されていて,バッファを介して BLANCA のローカル・バスにも接続されています. ElKit-BF533で搭載している ADSP-BF533 は PCIバス

を持っていないので、BLANCAのPCIバスには接続されません。図2のメモリ・マップを見ると分かるように、ADSP-BF533の非同期メモリ・バンクは合計で4Mバイトの空間しかありません。

CPU カード上のフラッシュ ROM はここに接続しています.しかし、そのままではすべての空間を占有してしまい、各種 I/O コントローラなどを接続できません.そこで ADSP-BF533 の GPIO (PF0)を1本使用し、バンク切り替えを行うことで回避しています.その処理は CPU ボード上の CPLD で行っています.

#### ● CPU コネクタ

BLANCA は FPGA で回路を構築するので、信号をどのようにピン・アサインしても対応可能です。しかし既存のピン・アサインにできるだけ合わせて割り当て、ADSP-BF533 には存在しない信号のピン (アドレス/データバスの上位ビットなど) には ADSP-BF533 固有の信号を割り当てています。ピン・アサイン

# 組み込みシステム 開発評価キット活用通信

E!Kit-BF533 の外観

#### 表 1 E!Kit-BF533 ボード仕様

| CPU      | Analog Devices 社 ADSP-BF533 600MHz    |

|----------|---------------------------------------|

|          | 16K バイト命令/32K バイト・データ・キャッシュ           |

| SDRAM    | 64M バイト× 16 ビット                       |

| フラッシュROM | 4M バイト× 16 ビット                        |

| シリアル     | UART×1(拡張ソケットにアサイン)                   |

| CPLD     | Xilinx 社 XC2C64A 100ピン                |

| JTAG     | 14 ピン                                 |

| 拡張ソケット   | 120 ピン× 2                             |

|          | CQ出版社製「組み込みシステム開発評価キット」対応             |

|          | 独自拡張ボード開発中                            |

| 温度特性     | 動作時:0℃~+50℃(周辺温度)                     |

| 電源       | $+3.3V \pm 5\%$ , max 1.0A            |

| 大きさ      | 100mm × 60mm                          |

| os       | uClinux 2.6 系カーネル (2.6.11 移植, 動作確認済み) |

|          | TOPPERS/JSP (μITRON 4.0 仕様準拠) 対応予定    |

は組み込みベースボード(CQ-BB100B)にも接続可能なように 考慮しています(稿末のコラム1参照).

#### ●クロック信号

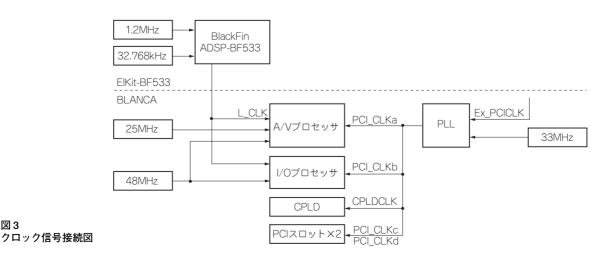

図3

図3はクロック信号の接続図です。E!Kit-BF533には ADSP-BF533のコア・クロック用の12MHzの水晶発振子と、RTC

| 00000000h r |                                                  |

|-------------|--------------------------------------------------|

| 08000000h   | SDRAM(64Mパイト)                                    |

| 04000000h   | (64M/\(\frac{1}{1}\)                             |

| 20000000h   |                                                  |

| 20100000h   | 非同期メモリ・バンクO(1Mバイト)                               |

| 20200000h   | 非同期メモリ・バンク1(1Mバイト)                               |

| 20300000h   | 非同期メモリ・バンク2(1Mバイト)                               |

| 20400000h   | 非同期メモリ・パンク3(1Mパイト)                               |

|             |                                                  |

| FF800000h   | データ・バンクA SRAM(16Kパイト)                            |

| FF804000h   | データ・バンクA SRAM/キャッシュ(16Kバイト)                      |

| FF808000h   |                                                  |

| FF900000h   | データ・バンクB SRAM(16Kバイト)                            |

| FF904000h   | データ・バンクB SRAM/キャッシュ(16Kバイト)                      |

| FF908000h   | ) - y · N > 9 B SRAIW/ + 7 9 9 I (10 N / 1 1 1 ) |

| FFA00000h   |                                                  |

| FFA10000h   | インストラクション SRAM(64Kパイト)                           |

| FFA14000h   | データ・バンクB SRAM/キャッシュ(16Kパイト)                      |

| FFB00000h   |                                                  |

| FFB01000h   | スクラッチ・パッド SRAM(4Kバイト)                            |

|             |                                                  |

| FFC00000h   | システムMMR(2Mバイト)                                   |

| FFE00000h   | コアMMR(2Mバイト)                                     |

| FFFFFFFh L  |                                                  |

図2 ADSP-BF533のメモリ・マップ

(Real-Time Clock) 用の 32.768kHz の水晶発振子が接続されて います. BLANCA には 48MHz, 25MHz の発振器がそれぞれ A/V プロセッサ、I/O プロセッサに接続されています。またPC IやCPLDの動作に使用する33MHzもあります.

E!Kit-BF533 は PCI バスを持たないので、BLANCA との接 続ではローカル・バス・クロック (L\_CLK) のみが接続されて います.

### ●リセット信号

図4はリセット信号の接続図です。BLANCAのリセット信

Interface Nov. 2008 149