第9章

# ミックスト・シグナル回路検証を体験する

■Dolphin Integration 社のミックスト・シグナル回路シミュレータ「SMASH I■

### 倉重克己

ここではミックスト・シグナル(アナログ・ディジタル混在)回路の検証工程 を体験していただきます、最近ではアナログ回路のモデリングにVHDL-AMSなどの設計言語が利用され始めています。そこで、本チュートリアル ではVHDL-AMSやC言語を利用したアナログ・ビヘイビア記述について触 れます. ここで使用するツールは、フランスDolphin Integration社のミッ クスト・シグナル回路シミュレータ[SMASH]です。このツールはVHDLや Verilog HDLのディジタル・モデル、およびSPICEのアナログ・モデルも 取り扱えます。本シミュレータの評価版とサンプル回路は、本誌付属のCD-ROMに収録されています. (編集部)

ボードの記事

現在では、一つのシリコン・チップ上にディジタル回路 とアナログ回路が混在していることは珍しくありません.

従来、こうしたチップを検証する際には、ディジタル部 とアナログ部を別々にシミュレーションし、両者のインタ ーフェース部については試作チップを製作してその整合性 を確認することが一般的でした。また、アナログ回路の規 模が大きいチップの場合、SPICEシミュレーションに膨大 な時間がかかります。 そのため、チップ全体のシミュレー ションを十分に行わないまま、試作チップを製造して動作 を確認することも珍しくありませんでした。当然のことな がら、試作チップを製造すると、コストと時間がかかりま す. そこで、ディジタル回路とアナログ回路の結合シミュ レーションやチップ全体のシミュレーションは必要不可欠 となってきています.

最近のミックスト・シグナル対応の回路シミュレータは、 このような場合のモデリングやシミュレーションに対応し ています。ディジタル信号とアナログ信号を結合する機構 や、広い抽象度をカバーするモデリング環境がEDAベン ダから提供され、ミックスト・シグナルのトップダウン設 計も現実のものとなってきました.

SPICEはアナログ回路検証の絶対的な標準ですが、設計 抽象度という点では低い水準の表現にしか対応していませ ん、そこで、SPICEとVHDL-AMS(VHDLのアナログ/ミ ックスト・シグナル拡張)を組み合わせて、SPICEの資産 の継承と、幅広い設計抽象度を利用したモデリングを両立 させる手法が提案されています. 本記事では、こうした SPICEやVHDL-AMSのモデル、さらにはディジタル用の ハードウェア記述言語であるVHDLやVerilog HDLのモデ ルを組み合わせて検証する手法について解説します。

## 使用するツールとサンプル回路

まず、本チュートリアルで使用するツールとサンプル回 路について紹介します.

### ●複数の言語に対応した回路シミュレータを利用

本チュートリアルではフランスのDolphin Integration社 が開発した「SMASH」を使用します。これは、VHDL-AMS、

### 〔表1〕 各設計言語の比較

設計分野別に異なる設計言語があり、歴史の長 い言語は多くの設計資産を抱えている. 回路規 模が拡大し、設計資産の再利用が重要な課題に なっている. そのため、多くの言語を取り扱え る設計環境が求められている。

| 設計言語        | VHDL,<br>Verilog HDL                | VHDL-AMS,<br>Verilog-AMS     | SPICE      | C言語                               |

|-------------|-------------------------------------|------------------------------|------------|-----------------------------------|

| 信号の種類       | ディジタル                               | アナログ                         | アナログ       | アナログ、ディジタル                        |

| 設計抽象度       | ビヘイビア・レベル<br>〜ゲート・レベル<br>(スイッチ・レベル) | ビヘイビア・レベル<br>~トランジスタ・<br>レベル | トランジスタ・レベル | アルゴリズム・レベル<br>〜ビヘイビア・レベル<br>(RTL) |

| 普及度         | 普及している                              | まだ普及していない                    | 普及している     | まだ普及していない                         |

| 過去の<br>設計資産 | 多い                                  | 少ない                          | 多い         | 少ない (アルゴリズム・<br>レベルの資産は多い)        |

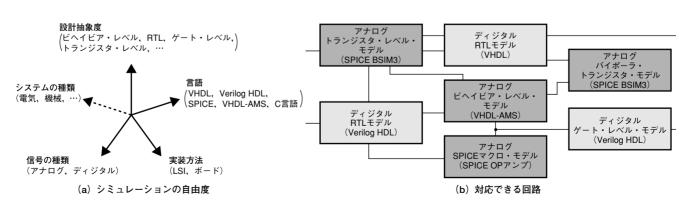

SPICE (Berkeley Spice 2G互换), VHDL, Verilog HDL, C言語といった複数の設計言語(記述フォーマット)に対応 したミックスト・シグナル回路シミュレータです。 本シミ ュレータが対応する言語の概要を表1にまとめます。また、 本シミュレータには図1(a)のような自由度があるので、図 1(b) のようなモデルを一括して検証できます.

こうした複数の言語に対応したミックスト・シグナル回 路シミュレータには、以下のような利点があります。

### 1) シミュレーション速度が上がる

設計抽象度の高いモデルは、シミュレーションに対する 負荷が小さいので、一般にシミュレーション速度が上がり ます。シミュレーション速度が上がれば、チップ全体のシ ミュレーションも行いやすくなります.

### 2) 動作を確認しながら段階的に回路を実現できる

設計抽象度の高いモデルを作成して, まず仕様の確認や 実現方法の検討を行い、その後、徐々に抽象度を落としな がら回路構成を決めていくことができます.

## 3) ディジタルとアナログの両方を含む回路を検証できる アナログ部はVHDL-AMS (またはSPICE) でモデリング し、ディジタル部はVHDLでモデリングすれば、ディジタ

ル回路とアナログ回路をいっしょに検証できます.

#### 4) 過去の設計資産やIPコアを扱いやすい

過去の設計資産は、多くの場合、SPICEやVHDL、Verilog HDLで作成されています、そのため、ほとんどのモデルを 本シミュレータに取り込むことができます.

#### 5) LSIだけでなくボード全体を検証できる

OPアンプや74シリーズなどのモデルが用意されている ので、ボード全体をモデリングすることが可能です。

### 6)機械系などと結合してシミュレーションできる

VHDL-AMSは、電気系だけでなく、機械系や流体系など のモデリングにも対応しています。そのため、本シミュレ ータを自動車の電装系やMEMS (micro electro mechanical systems;シリコン技術を使ったマイクロマシン)のモデリ ングやシミュレーションにも利用できます.

なお、SMASH 5.0.0評価版 (ライセンスがない状態の機 能限定版)のインストール方法、および回路規模の制限に ついては、付属CD-ROMに収録されているreadme1st.txt (SMASHが収録されたフォルダにある)を参照してください。

### ●サンプル回路はAMS, Verilog, SPICE, Cの組み合わせ このチュートリアルのサンプル回路は、いろいろな言語 のわかりやすいモジュールを集めたものです(回路的には あまり意味はない). VHDL-AMS, Verilog HDL, SPICE, C言語の各モデルを含み、プリント基板とLSIの両方にま たがるミックスト・シグナルの小さな設計例です。SMASH 5.0.0評価版でも問題なくシミュレーションを実行できます.

### ミックスト・シグナル・シミュレーションの実際

本誌付属のCD-ROMには「SMASH操作チュートリアル」 というpdfファイル(本記事関連データが収録されているデ ィレクトリの下のrcフォルダの中のtut rc.PDF) が収録さ れています。まず、これを確認して、本シミュレータの操 作の基本とSPICEシミュレータとしての使いかたを理解し てください. 収録されているチュートリアルでは、図2(a) の回路の動作点解析、過渡解析、AC解析、パラメータ・ス

〔図1〕SMASHにおけるシミュレーションの自由度

ミックスト・シグナル回路シミュレーションには,高い自由度が要求される.SMASHは,(a)に示すように,多様な設計抽象度,多様な言語,LSI実装/ボード実 装、アナログ信号/ディジタル信号を取り扱うことができる、そのため、(b)のようなモデルを一括してシミュレーションできる。