# 学習用マイコン・ボードの製作

FPGA向け32ビットRISC CPUコア 「Nios」を活用する 藤村雅

藤村雅志, 仁木知記

ここではFPGA向けのCPUコアを使用した汎用マイコン・モジュールを製作する。CPUコアには、米国Altera社の「Nios」を使用する。パラレルI/O、シリアルI/O、タイマなど、基本的な周辺機能を統合する。付属のFPGA基板を、汎用の32ビット・マイコンとして利用できるようになる。また、このモジュールを使ったマイコン・ボードを製作する。(編集部)

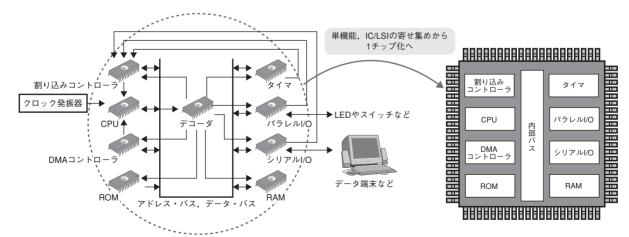

米国Intel社の8080や米国Motorola社の6800, そして米国Zilog社のZ80を代表とする8ビット・マイコン全盛の時代は、たくさんのIC/LSIを組み合わせて一つのマイコン・システムを実現していました。CPU、パラレルI/O、シリアルI/O、タイマ、DMA (direct memory access) コントローラ、割り込みコントローラなどの周辺機能はそれぞれ独立したLSIであり、メモリは複数のチップで構成されていました。また、アドレス・デコーダなどは汎用のTTL

ICを組み合わせたものでした. 一つのシステムを実現する ために複数のボードを必要とする場合も多く, 物理的にも 大きなものでした.

その後、LSIの高集積化が進み、ルネサステクノロジのSHマイコンをはじめとする32ビットRISCプロセッサ全盛の今では、CPUに多くの周辺I/Oが統合されるようになりました。ASIC設計においてもCPUコアが使われるようになり、特定のシステムに必要なすべての機能を1チップ化するSOC(system on a chip)の時代になっています(図1). そして、ASICのみならず、FPGAであってもSOCを実現できる時代を迎えました。手元のパソコンで、GUI(graphical user interface)ベースのツールを操作するだけで、SOCを設計できます。本誌付属の基板に搭載されている EP1C3は、LE(Logic Element)数が 2,910個というCycloneファミリの中ではいちばん小規模のデバイスです

〔図1〕昔のマイコン・システムと現在のSOC

ひと昔前は、CPU、パラレルI/O、シリアルI/O、タイマ、DMA (direct memory access) コントローラ、割り込みコントローラなどの周辺機能はそれぞれ独立したLSIであり、メモリは複数のチップで構成されていた。現在は、CPUに多くの周辺I/Oが統合されるようになり、特定のシステムで必要とされるすべての機能の1チップ化が進んでいる。

## 付属FPGA基板を使った 回路設計チュートリアル

が、それでもSOCを実現できるのです。

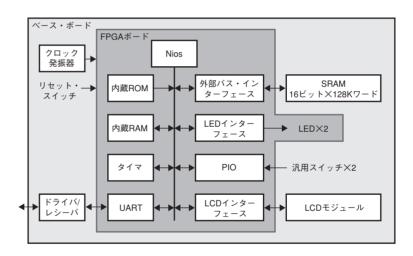

本稿では、EP1C3に米国Altera社のソフト・マクロCPUである「Nios」を組み込み、図2のような学習用マイコン・システムを構築します。

## FPGAにCPUコアを組み込む

マイコン・システムの機能のうち、FPGAにはCPUコア、ROM、RAM、タイマ、UART、外部バス・インターフェース、LED用出力ポート、スイッチ用入力ポート、LCDモジュール・インターフェースを組み込みます。使用したNios内部コンポーネントの詳細を図3に示します。モジュール名は、わかりやすくするためにデフォルト値から変更してあります。

すべての機能は、Altera社が提供するNiosの開発環境

「Nios Development Kit (NDK)」<sup>注1</sup>に標準で添付されている モジュールだけで実現しました。最上位階層のブロック接 続を行っただけで、論理回路設計らしいことはまったく行 っていません。GUIによる簡単な操作だけで設計しました。

FPGAの最上位階層の回路図を図4に示します。クロック入力とNiosモジュールの間にPLLを挿入しています。今回は1:1の分周比で使用しているので実際には不要ですが、クロック周波数を調整したい場合を想定して入れておきました。2てい倍(66.6666MHz)における動作も確認しています。

今回使用したCycloneデバイスのスピード・グレードはファミリの中でいちばん遅いものですが、回路の最適化などを行わなくても80MHzを超えるタイミング・レポートを得ています。チューニングすればどこまで性能が上げられるのか、時間があれば確かめてみたいと考えています。

### 〔図2〕 <mark>学習用マイコン・システムのブロック図</mark> EP1C3にAltera社のソフト・マクロCPUである 「Nios」を組み込んだ。

#### 〔図3〕

#### Niosの内部コンポーネント一覧

Niosの開発で使用する SOPC Builderの画面である。 SOPC Builderは、Quartus II 3.0に統合されている。ここではCPUコア、ROM、RAM、タイマ、UART、外部バス・インターフェース、LED用出力ポート、スイッチ用入力ポート、LCDモジュール・インターフェースを組み込んでいる。モジュール名は、わかりやすくするためにデフォルト値から変更しているものがある。

|     |   |    |   | PU: | struction_master (avalon)<br>2 / data_master (avalon)<br>bri_state_bridge_0 (avalor |                                     |          |             |    |

|-----|---|----|---|-----|-------------------------------------------------------------------------------------|-------------------------------------|----------|-------------|----|

| Use | П | Т  | Т | Ħ   | Module Name                                                                         | Description B                       | lase     | End         | Ro |

| V   | П | П  | П | Т   | ⊞ CPU32                                                                             | Nios Processor - Altera Corporation | 111111   | 11111111    | 77 |

| V   | н | Η. | н | Ή   | boot_monitor_rom                                                                    | On-Chip Memory (RAM or ROM) Bx0     | 00000000 | 0x000007FF  | 77 |

| V   | В | Η. | н | Έ   | ⊞ uart1                                                                             | UART (RS-232 serial port) Batt      | 00000000 | 0x0000081F  | 17 |

| V   | В | #  | H | Έ   | ⊞ lcd_pio                                                                           | PIO (Parallel I/O) But              | 00000820 | 0x0000082F  | 77 |

| V   | В | #  | H | Έ   | ⊞ button_pio                                                                        | PIO (Panallel I/O) (bat)            | 00000830 | 0x0000083F  | 18 |

| V   | В | #  | H | Έ   | ⊞ timer1                                                                            | Interval timer (but                 | 00000840 | 0×00000085F | 16 |

| V   | В | #  | H | Έ   | ⊞ led_do                                                                            | PIO (Panallel I/O) (but)            | 00000860 | 0x0000086F  | 77 |

| V   | н | -  | н | Έ   | <b>⊞</b> onchip memory 0                                                            | On-Chip Memory (RAM or ROM) 8x6     | 00001000 | 0x000017FF  | 77 |

| V   | н | -  |   | Ή   | ⊞ tri state bridge 0                                                                | Avalon Tri-State Bridge             | 1111111  | 111111111   | 00 |

| N   | П | -  | ₽ | ٠   | ⊞ ext_ram                                                                           | Interface to User Logic 0x0         | 00040000 | 0x0007FFFF  | 77 |

注1: Niosを搭載するシステムを開発するためには、開発キットのNDKを入手する必要がある。定価は995ドルである。日本の代理店では通常14万円程度で販売されている。このキットを購入することで、Niosの正規ライセンスを取得したことになり、ロイヤリティ・フリーで使用できる。今回設計したFPGA向け回路データ(SOFおよびPOFファイル)は、本誌付属のCD-ROMに収録してある。