# 高速ディジタル回路設計のための アナログ回路シミュレーションλ門

第8回

# SPICEを使った - - インテグリティの解析(前編)

渡邊貴之,浅井秀樹

今回からは、電源系のノイズを解析する方法について解説 する. 具体的には、電圧レギュレータやデカップリング・ コンデンサをモデル化し、SPICEによって解析する.ディ ジタル回路の動作クロックの上昇とともに、ボードやチッ プ内の電源系のノイズの影響が問題となってきている. チ ップ内配線については、寄生インダクタンス成分について も配慮する必要がある. (編集部)

本連載でこれまで説明してきたように, シグナル・イン テグリティ(信号の品質)を検証するためには,ボード上の 配線やケーブルを伝送線路としてモデル化し, SPICE<sup>(1)</sup>な どのツールを用いてシミュレーションを行います.

これとは別に、パワー・インテグリティという概念があ ります、これは電源やグラウンドの品質を意味しています、 パワー・インテグリティの検証では,ボードの電源/グラ ウンド・プレーンを2次元的または3次元的にモデル化し, デカップリング・コンデンサやLSI の電源モデル,電源レ ギュレータのモデルを付加して解析を行います.

今回からは, SPICE を使ったパワー・インテグリティの 解析方法についてご紹介します.

## ● 片面, 両面基板では伝送線路構造を作るのが難しい

さて,本連載の第5回~第7回<sup>注1</sup>では,ボード上の配線

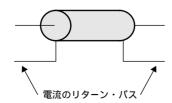

図 1 伝送線路の標準的な回路図シン ボル

伝送線路モデル(single line)は,か ならず4端子素子として表される.

を伝送線路としてモデル化するためのモデル・パラメータ の抽出方法について紹介しました. ところで, どのような 配線であっても伝送線路としてモデル化することができる のでしょうか?

配線がマイクロストリップやストリップ、コプレーナと いった線路構造をとっているのであれば、伝送線路として モデル化できます、しかし、電源やグラウンドがベタ・プ レーンとなっている4層以上の多層ボードでなければ、マ イクロストリップ線路を構成することは難しいでしょう(も っとも, 多層ボードであっても最近はプレーンにビア穴が 無数にあいており、きれいなマイクロストリップ線路には ならないが...). RF(高周波)電流が伝わる信号ラインとそ のリターン・パス(電源ラインまたはグラウンド・ライン) の断面形状が電流の進行方向に対して変化しないことが、 伝送線路としてモデル化できる前提条件なのです. 例えば, 図1のような伝送線路の標準的な回路図シンボルでは,電 流のリターン・パスが端子としてかならず描かれています.

このように片面基板や両面基板では,意図的に伝送線路 の構造を作らないかぎり、RF電流のリターン・パスがど こになるのかを特定することは難しいと思います、もしも 伝送線路の構造を持たない配線に無理やり高速信号を入力 したとしても、配線がアンテナとなって電磁波が放射され るだけで, まともに信号を伝送できません.

#### ● ディジタル・チップ内の配線も伝送線路構造へ

「チップ内の配線でもインダクタンス(L)成分の影響が問

注1:第5回は本誌2003年4月号のpp.140-146に,第6回は2003年7月号の pp.123-128 に,第7回は2003年10月号のpp.142-148 に掲載された.

題となってきた」、「チップ全体を引き回すような長い配線 では,インダクタンスを考慮する必要がある」といった声 が1990年代後半から高速ディジタル回路の分野で聞かれる ようになってきました. それとともに,「配線のシミュレ -ションにLを含めるために、どうやってチップ内配線の L成分を高速に抽出するか」という研究が広く行われていま す. 一般に, Lの抽出はキャパシタンス(C)の抽出よりも 煩雑です.

ところで, 基板専門の技術者だと, 「L成分を抽出しなく ても、配線の単位長さ当たりのC成分がわかれば公式から Lを計算できるのでは?」と考えてしまうかもしれません.

$$L = \frac{\varepsilon_r}{v_0^2 C} \tag{1}$$

ここで, vo は光速, は比誘電率を示しています. もち ろん,この公式が使えるのは,配線がTEM(transverse electro-magnetic )波や準 TEM 波を伝送する伝送線路の構 造になっている場合のみであって、一般にはそう単純では ありません、チップ内では、RF電流のリターン・パスが 電源/グラウンド・グリッドなのか、ほかの信号配線なの かを特定することが難しいため, L成分を詳細に抽出する 必要があるのです.

チップ内のローカルな配線は, 伝送線路の構造を採用し ていなくても信号波長に対して十分に短いので問題ありま せん.しかし,チップ全体を引き回すようなグローバル配 線(データ・バス,クロック・ライン,電源配線など)では L成分の影響が現れるため, そのままではシグナル・イン テグリティの確保が困難となります.

一方, MMIC( monolithic microwave IC )のような高周 波/マイクロ波用のアナログ IC では,チップ内であっても あたりまえのように伝送線路構造が採用されています.「そ れなら,ディジタルICでも伝送線路構造を意図的に作れば よいのでは?」ということで,実際に,最近の高速なマイ

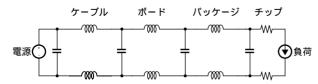

図2 一般的な電源系(PDS)の模式図

電源系における寄生成分については、チップ内は主に抵抗成分を、チップ外 は主にインダクタンス成分を考慮する必要がある.また,各レベルでデカッ プリング・コンデンサを挿入している.

クロプロセッサなどでは、クロック・ラインにコプレーナ 構造が採用されたり、電源グリッドが伝送線路的に配置さ れたりしています.

### ● 電源系のインピーダンス目標値を設定する

高速ディジタル回路用のボードの伝送線路解析では,配 線のビア部やコネクタ部について特別な配慮が必要です. すなわち,別途,その部分のRLC成分を抽出して,RLCの 集中定数回路(等価回路)を作成し,ほかの部分の伝送線路 モデルと組み合わせて解析することになります.

シグナル・インテグリティは、電源系(PDS:power distribution system )の品質の影響を受けます.ここで, ひと口に電源系と言っても,チップ内から電源レギュレー タまで,複数のステージが存在します(図2).

チップ内を流れる電流がなんらかの要因で変動すると、 電源/グラウンド・パスのインピーダンスによって供給電 位が変動します.このインピーダンスは,チップ内では抵 抗成分Rが主ですが、パッケージやボードではインダクタ ンス成分Lが主となります、Lの効果は電流の時間変化 (di/dt)に比例して効くので,短時間に大きく電流が変動す ると、チップに供給される電源電圧が大きく低下します(こ の現象を rail collapse と呼ぶ). そのため,信号配線におけ る遅延やクロストーク,減衰,反射の検証だけでなく,電 源/グラウンド配線を抜き出してノイズ解析を行うパワー・ インテグリティの検証も重要となっています.

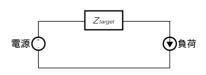

電源系のノイズを低減させるためには,よく言われてい るように電源/グラウンド・パスのインピーダンス(抵抗成分 とインダクタンス成分)を最小化し,電圧の変動を抑えるた めのデカップリング・コンデンサを複数個配置します<sup>(2),(4)</sup>. そのためには,まず所望のノイズ・レベルを満たす,負荷 側から電源系を見たときのインピーダンス目標値 Zurget を設 定します(図3).

例えば,チップの電源電圧を $V_{DD}$ ,過渡的な電流変動を

図3 インピーダンス目標値を設定する

パワー・インテグリティでは, 所望のノイズ・レベルを満たす, 負荷(チップ) 側から電源系を見たときの最大のインピーダンスを目標値として設定する.