|

1.上流設計用EDA(論理設計,システム設計)

(株)東芝 セミコンダクター社

システムLSI設計技術統括部 西尾 誠一 |

半導体の微細化技術の目覚しい向上により,1チップ上に数十Mゲートもの論理を搭載したシステムLSIが製造可能となってきた.これまで複数のチップを必要とした専用ハードウェア,周辺回路,プロセッサやプロセッサで実行するソフトウェアを格納するメモリが,1チップ上に実現できるSoC(System on a Chip)時代に入ったのである.このような大規模かつ複雑なシステムLSIを市場要求に見合った短工期で開発するためには,従来の設計手法・ツールではまかないきれなくなってきている.21世紀を迎えて,新たな設計パラダイムが必要となったのである.このためのキーとなる手段としては,下記の3つがある.

(1)設計抽象度の向上: 80年代の後半に,ゲートレベル設計からRTL設計に設計の抽象度を上げて設計効率を向上させたように,RTL設計よりもさらに設計抽象度の高いレベルで設計を進めることを可能として,設計効率をもう一段向上させるための手法.

(2)部品化: IP (intellectual property)と呼ばれるようなハードウェア部品や,ミドルウェアと呼ばれるようなソフトウェア部品を再利用して設計効率を上げる手法.

(3)設計手戻りの削減: 設計工程が進んでから,要求性能が達成できないとか,前の設計工程のバグが検出されるなどの理由による,設計工程をさかのぼってのやり直しを削減するための手法.たとえば,デザイン・プランニングと呼ばれるような技術がこれに相当する.

以下,本稿では,おもに設計抽象度の向上の部分に焦点をあてて,高位設計のためのEDA技術・ツールを紹介する.

● システム仕様記述

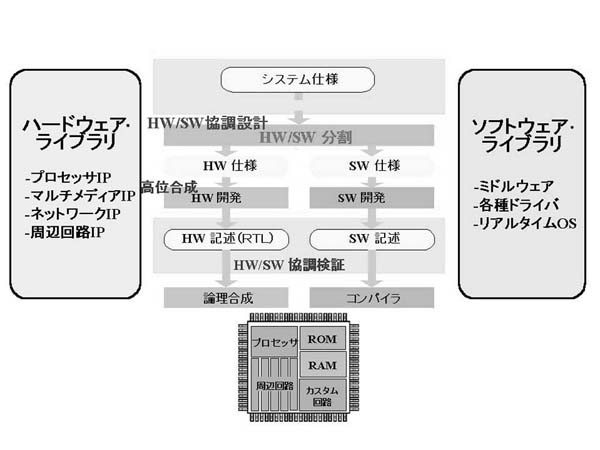

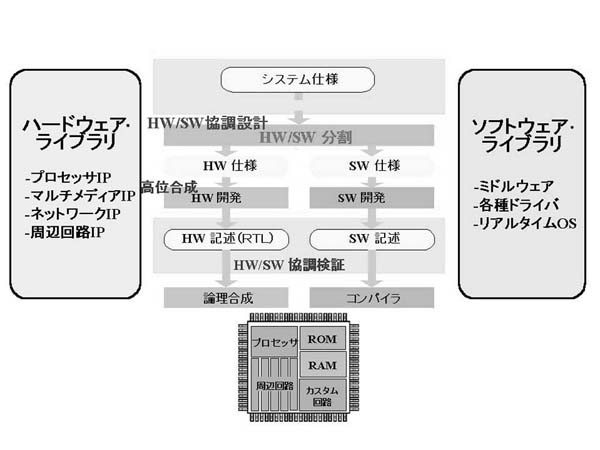

現在考えられ始めている高位からの設計フローを図1に示す.ここでは,まずハードウェアで実現する部分,ソフトウェアで実現する部分を切り分ける前のシステム全体の仕様を記述できる新たな言語が必要となる.このための言語標準化に向けて,いくつかの言語が提案されている.おもなものとしては,EDAベンダを中心に提案されたSystemC,組み込み業界が中心となって提案されたSpecC,Co-Design Automation社が中心となって提案されたSuperlogなどがある.SystemCは,C++言語をベースにハードウェアの記述用にクラス・ライブラリを追加したものであり,当初はハードウェア部分の仕様記述用のレベルであったが,順次拡張されつつある.SpecCは,C言語をベースに並列性や,モジュール間の通信の概念などを追加したものであり,ソリトンシステムズなどからこの言語をサポートするツールが提供され始めている.また,Superlogは,Verilog HDLとC言語を合体したような言語であり,現在のRTL設計との親和性のよさから,まずハードウェア仕様の記述用として広まる可能性もある.問題は,現時点ではどの言語が標準となるかがはっきりしていないことにある.今日のEDA業界の隆盛は,Verilog HDL,VHDLという標準言語が定まったことに負う部分が大きいわけであり,システム仕様の記述言語に関しても,ぜひ各社とも私利私欲を捨てて,真に有用な標準言語の策定に向けて注力していただきたい.

図1 高位からの設計フロー

SystemCをサポートするツール群の代表的なものとしては,CoCentricファミリ(Synopsys社)があるが,このなかの技術としては浮動小数点を用いて書かれたソース記述を解析して固定小数点のコードに変換するCoCentric Fixed-Point Designerに注目したい.また,設計者のRTLから高位言語への移行を容易にする工夫も重要であるが,このためのツールとしてVisual HDLの高位版であるVisual SLD (Innoveda社)が発表されている.

●ハードウェア/ソフトウェア協調設計(Co-design)ツール

システム仕様が決定されると,所望の性能,コストに見合った設計とするために,ハードウェアで実現する部分とソフトウェアで実現する部分との切り分けを行う必要がある.この部分に関しては,自動的に最適解を求められるような技術はまだ実用レベルに達していない.しかし,設計者が切り分けの案を決定した際に,その設計案の性能を解析し,性能確認やシステム・ボトルネックの解析などができるツールは実用になり始めている.市販ツールとしては,VCC (Cadence社),Forsight (Nuthena社)などがある.

●ハードウェア/ソフトウェア協調検証(Co-verification)ツール

ハードウェア/ソフトウェアの切り分けが完了すると,後はそれぞれの部分の設計を進めることになるが,設計が完了してから,たとえばハードウェア・ソフトウェア間の通信などの部分で不具合が見つかると,設計の手戻りが発生してしまう.この問題を回避するためのツールとして,ハードウェア/ソフトウェア協調検証ツールがある.このツールでは,ハードウェアとソフトウェアの双方を同期を取りながらシミュレーションするものであり,SeamlessCVE (Mentor社),Eagle-i (Synopsys社),仮想ICE(横河電気),ASVP(Cynergy社)などのツールが実用に供されている.これらのツールは,おおむねサイクル精度でソフトウェア部分の機能を受けもつターゲット・プロセッサをシミュレーションするものである.最近の動向としては,協調検証の効率向上を目指して,Specman Elite (Verisity社),Vera (Synopsys社)などのテストベンチ開発環境との統合が進められている.

上記のハードウェア/ソフトウェア協調検証ツールは,ハードウェア部分や,デバイス・ドライバの検証に適しているが,応用ソフトウェア全体の検証に適用するのは,シミュレーション速度の点から一般に困難であった.これに対して,最近では応用ソフトウェア全体の検証に適したツールとして,CoMET (VaST社)が発表されている.CoMETでは,モデル化の抽象度をより高めることにより,20MIPS程度のシミュレーション速度を達成しているという.

●高位合成・動作合成ツール

Verilog HDLのビヘイビア記述,C/C++言語,あるいは上述の新たなシステム仕様記述言語で書かれたハードウェア部分の仕様記述から,RTLを自動的に合成するツールが高位合成・動作合成ツールである.ArchiMate (ArexSys社),System Compiler (C-Level社),N2C (CoWare社),Cynthesizer (CynApps社),A|RT Designer Pro (Frontier Design社),Design Prototyper (Future Design Automation社),VOLARE-Architectural Synthesis (get2chip社),SystemC Compiler,Behavioral Compiler (以上Synopsys社),eXplorations (Y Explorations社)など非常に多くのツールが発表されている.当初は,サイクルの切れ目を意識したレベルの記述からの合成機能のものが主であったが,最近ではより抽象度の高い記述からの合成が可能となってきており,今後急速に実用化が進むものと期待される.どのシステム仕様記述言語が標準になるかがまだ不明確な段階では導入しづらいという向きには,Design Prototyper,VOLARE,Behavioral CompilerなどのVerilog HDLビヘイビア記述を入力として受け付け可能な高位合成ツールからまず導入してみるという手もある.

●その他の上流設計用EDA

以下では,これまで言及しなかったツールのうち,特徴的なものをいくつか紹介する.

上述したように,システム仕様記述言語はまだ標準言語が定まってはいないが,現在提案されているものはいずれもC/C++ベースのものである.とくに,現在のRTL設計からの移行の過渡期においては,仕様記述とRTL記述が混在するような設計となることが予想される.このような設計において有効となりそうなツールとして,AfterBurner (Cynergy社),SystemSim (Co-Design社)がある.AfterBurnerは,Verilog HDLのRTL記述を入力として,サイクル精度のCモデルを生成するツールである.また,SystemSimは,C/C++,Verilog HDL,SystemC, Superlogなどの混在する設計をPLIを介さずに単一カーネルで実行可能なシミュレータであり,混在時のシミュレーションを小さなオーバヘッドで実行できる点に特徴がある.

また,携帯情報機器向けなどの分野のシステムLSIでは,バッテリ寿命の関係から,ローパワー化ということが非常に重要となってきている.最上流では,上述のVCC (Cedence社)が,消費電力のモデリング支援を開始している.また,RTLレベルでは,WattWatcher,PeakWatcher,WattSmith (以上Sequence Design社)などのツール群がある.このツール群では,RTL設計段階でパワーを見積もることができ,パワー削減のためのRTLコードの変更方法についてのガイダンスも得ることができる.

2. 下流設計用EDA(ディジタル・レイアウト設計)

三洋電機(株)セミコンダクターカンパニー

システムLSI事業部 箱田 俊幸 |

LSI製造プロセスの微細化およびそれによる市場の変化にともない,次のような問題が顕在化してきている.

- 動作速度に対し,論理ゲート遅延に比べて配線遅延が支配的

- 配線容量は縦構造ではなく横方向が支配的

- 集積度の向上により,単位面積あたりの消費電力が増大

- PCをはじめ多くの応用分野がLSIに高性能化を要求

- LSIのシステム化にともない,1チップに集積される素子数が増大

これらの課題に対応するために,ここ数年新たなレイアウト技術が開発されている.新技術のおもな動向は個別ツールで行っていた処理を統合化し全体的な最適化を行おうとするものである.従来,シーケンシャルに行われていたタイミング収束やシグナル・インテグリティにかかわる問題を同時並行的に解決している.すなわち,配置→クロック・ツリー合成→セットアップ/ホールド・バイオレーション改善→クロストーク・電源線のIRドロップなどによるタイミング劣化の修正→概略配線→詳細配線を独立に行っていたものを相互作用を考慮しつつ,同一エンジンで最適化している.統合化のレベルとしては,ネットリスト以降とRTL以降に大別される.

●ネットリスト以降の統合化

基本的にはフロントエンド設計には手を加えず,バックエンドのみで課題を解決することになる.したがって,論理設計者の負担が増大せず現状フローとの整合性もきわめてよいため,いま現在ではもっとも適用されていると思われる.ツールに入力する論理情報はゲート・レベルであるが,最適化の過程で必要に応じたんなるバッファ・インサーションだけではなく,リマッピングを含む積極的な回路変更を行う.このとき,論理情報のみを残してすべてのタイミングを最適化し直すツールも発表されている.

これらのツールにおける最大の問題は,論理設計時点での性能予測が困難な点である.一般的には論理合成における配線負荷の見積もりは悲観的に設定されるため,レイアウト不能とはならないが,最適なアーキテクチャを選択できないことになる.

●RTL以降の統合化

現在の合成技術は配線負荷が論理ゲートのファンアウトの関数となっているため,本質的に微細化に対応できない.これを補うため,配線によるタイミングの問題を論理合成時点から配慮するPhysical Synthesisと呼ばれる手法が出てきた.これは論理合成と配置・概略配線程度までが一体となるため,従来の論理設計者とレイアウト設計者の協調が重要となる.また,合成単位のブロックのみではなくスキャン・パスを含めたチップ全体の正確なタイミング制約が必須となる.

技術的には現在の仮合成→配置→カスタム・ワイヤ・ロード・モデル→再合成のループを同一エンジン内で高速に行い,最適配置を短時間に作り出すものである.したがって,根本的には論理合成がもっている問題を解決しているわけではなく,最適化のルーチンを設計者から隠しただけともと言える.しかし,当然ながらPhysical Synthesis後の配置結果は詳細配線後のタイミング検証を満たす可能性がきわめて高いため,1パスでレイアウトを終了することが期待できる.

これらのレイアウト手法の基盤には配線の寄性RC抽出,遅延計算,消費電力見積もりなどの高精度化が要求される.また,たとえば抽出技術は0.5μm時代の2次元→寄生2.5次元→3次元と複雑化し,素子数の増大により膨大な量のデータ処理が必要となっているため,レイアウト・ツールのデータベース設計も重要となっている.各EDAベンダともフロー全体に渡る配線の寄生RC,遅延,消費電力などを統一的に扱いかつ軽く,インクリメンタルな処理に対応できるようなデータベース設計を行っている.

さらに大規模なSoCを設計するため,チップ全体をフラットに処理することが現実的ではなくなるため,階層設計のアプローチも開発されている.

3. 下流設計用EDA(アナログ・レイアウト設計)

三洋電機(株)セミコンダクターカンパニー

システムLSI事業部 加藤 政美 |

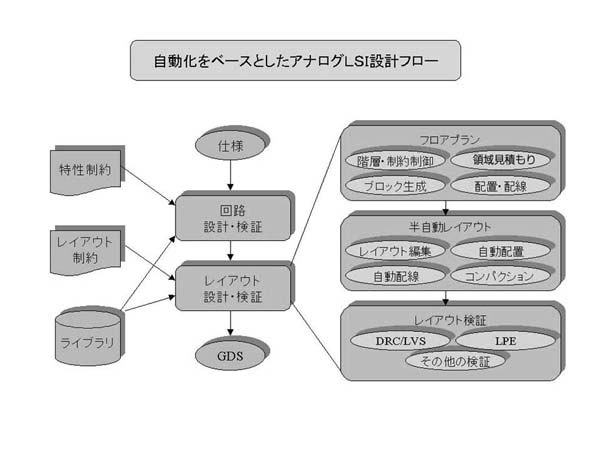

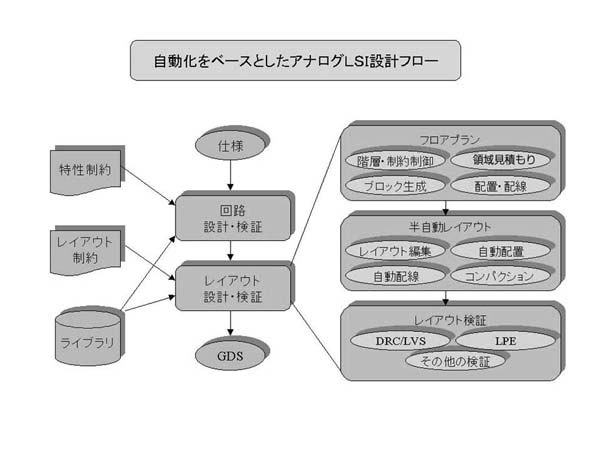

バイポーラ/BiCMOS/CMOSプロセスを用いたアナログ・レイアウト設計においては目標特性や目標チップ・サイズが厳しい場合が多く,まだ手設計に依存する領域が多い.自動設計ツールもレイアウト制約や素子形状の多様性により実用化がむずかしく,ディジタルと比較して歩みは遅い.このため,設計フローを大きく変革するまでには至っていない.とはいえ,急進するディジタル設計技術に牽引されながらアナログ設計に目を向けたツールが徐々に増えてきており,自動化をベースとしたフロー改革の可能性が出てきている(図2).

図2 自動化をベースとしたアナログLSI設計フロー

●レイアウト・エディタ/フロアプラン・ツール

アナログのレイアウト・エディタはレイアウト設計の基本ツールである.上流から渡されるネットリストにしたがって対話的なレイアウト編集を行う.設計変更に対応するためECO(engineering change order)は必須の機能である.また素子設計のための基本的な素子生成機能やプログラム記述による素子発生が可能となっている.小規模なLSIのフロアプランはレイアウト・エディタを用いて行われるが,大規模なLSIの設計ではトップダウン設計を可能とするフロアプラン・ツールが使用される.フロアプラン・ツールの機能として配置・配線領域見積り,ブロック生成と最適端子配置,ブロック自動配置・配線などがある.これに加えて,階層制御や制約制御の機能も盛り込まれつつある.

●自動設計ツール

アナログの自動設計ツールとして配置,配線,コンパクション・ツールがある.自動配置ツールは発展途上であり,まだ実用的に使用できるレベルではない.人手による修正やコンパクション・ツールの併用により最適配置する方法が一般的である.自動配線ツールは機能・性能が充実し,実用的に使用できるようになってきた.ブロック間配線では制約を付加した一括自動配線により,手設計に近い配線結果を短時間に得られるようになってきた.しかし,電源配線や素子間配線ではまだ人手による修正を必要とし,時間を要する.コンパクション・ツールはレイアウト面積最小化のために重要なツールであるが,配置・配線制約の重要なレイアウト設計においては,これらの制約を維持するように注意して使用する必要がある.今後,配置,配線,コンパクション・ツールは,一貫したレイアウト制約を保証できるように,制約マネージメント・ツールへの対応が必要となる.

●検証ツール

レイアウト検証ツールとしては,基本的なDRC(design rule check),LVS(layout versus schematic)に加えて,LPE(layout parameter extraction)の重要性が増している.高周波用途のLSI設計では寄生RC抽出の精度の向上とともにL抽出が必要となってきており,対応ツールの開発が進んでいる.その他の検証ツールとして,ミックスト・シグナルLSIで問題となるサブストレート・ノイズの解析ツールが使われ始めている.

●自動化と統合化の方向

アナログのレイアウト設計工程の自動化・統合化のためにはフロアプラン・ツールおよび自動レイアウト・ツールの機能向上が必要である.特にアナログ・ブロックやアナログ素子の自動最適配置はむずかしく全体の自動化を妨げている.また,レイアウト制約への対応が遅れているため,まだまだ人手の修正を必要とする半自動設計が現実のフローである.もう一つの流れとして上流設計ツールとの統合化がある.回路・レイアウト設計の一貫した設計環境は設計精度や設計効率を高める目的で導入が進んでいる.しかし,設計環境に必須なライブラリの開発がむずかしくなる問題もある.今後,ライブラリ開発のための支援ツールが重要となる.最近,アナログ向けのレイアウト合成ツールが登場し利用され始めているが,小規模なCMOSアナログ回路向きであり,使用用途は限定されている.

DESIGN WAVE MAGAZINEのホームページへ

DESIGN WAVE MAGAZINEのホームページへ

CQ出版のホームページへ

CQ出版のホームページへ

Copyright(C) 1996-2001 CQ Publishing Co., Ltd.

DESIGN WAVE MAGAZINEのホームページへ

DESIGN WAVE MAGAZINEのホームページへ