### 第8章

# ISE WebPACK 活用チュートリアル

ここでは、米国Xilinx 社のFPGA/PLD 開発ツール[ISE WebPACK 10.1i] の使い方を解説する、XC3S 250E 向けの簡単な回路を設計し、FPGA を動作させる、実際に行う手順を具体的に示すので、同じよ うに操作すれば FPGA 設計を体験できる (本書付属 DVD-ROM から開発ツールをインストールする手順 については、第8章 APPENDIXを参照). (編集部)

ここでは、ISE WebPACK 10.1 を使用して、プロジェクト作成から FPGA ヘダウンロードする手順を説 明します. ISE は Xilinx 社の FPGA/PLD 開発ツールです. もともとは Integrated Software Environment の略称であり、統合設計環境を意味しています。設計入力、論理合成、配置配線、タイミング解析、FPGA への回路データのダウンロードなど、FPGA 開発の一連の作業を行うことができます。

ISE WebPACK 10.1 は、本書付属 DVD-ROM に収録しています。 定期的にバージョンアップされてい ますが、最近は基本的な操作方法はほとんど変わっていないので、今後のバージョンでもある程度対応で きると思います.

## FPGA 基板とサンプル回路の準備

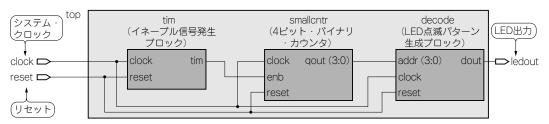

サンプル回路は、LED を点滅させる回路とします. 回路の構成を図1に示します.

回路は、top (リスト1)を最上位ブロックとして、三つの機能ブロックで構成しています。

smallcntr ブロック (リスト2) の4ビット・カウンタの値に従って、decode ブロック (リスト3) で生成し たパターンを出力し、LED を点滅させます.

使用する FPGA 基板には,33MHzのクロック発振器が実装されているものとします.このクロックを そのまま使用すると、LED の点滅動作を目で見ることができません。そこでtim ブロック (リスト4) では、 周期の長いイネーブル信号を作っています、smallcntr は、このイネーブル信号が"H"の時のみカウント アップするように動作します.

#### 図1 サンプル回路のブロック図

最上位ブロックとして、三つの機能ブロックで構成されている.

#### リスト1 最上位ブロック top のVHDL ソース・コード (top.vhd)

```

library ieee;

end component;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

component decode

use ieee.std_logic_unsigned.all;

port (addr: in std_logic_vector

(3 downto 0);

entity top is

clock: in std_logic;

port (clock : in std logic;

reset: in std logic;

reset : in std_logic;

dout: out std_logic);

ledout : out std_logic);

end component;

end top;

begin

architecture arc_top of top is

ul: tim port map(

signal cntout : std_logic_vector

clock => clock,

( 3 downto 0);

reset => reset,

signal enable : std_logic;

tim => enable);

component tim

u2: smallcntr port map(

port(clock : in std_logic;

clock => clock,

reset : in std_logic;

reset => reset,

tim : out std_logic);

enb => enable.

end component;

qout => cntout);

component smallcntr

u3 : decode port map (

port (clock : in std_logic;

addr => cntout,

reset : in std_logic;

clock => clock,

enb : in std logic;

reset => reset.

qout : out std_logic_vector

dout => ledout);

(3 downto 0));

end arc top;

```

#### リスト2 smallcntr ブロックのVHDL ソース・コード (smallcntr.vhd)

```

library ieee;

use ieee.std_logic_1164.all;

process (clock, reset)

use ieee.std_logic_arith.all;

begin

use ieee.std_logic_unsigned.all;

if reset='0' then

temp <= "0000";

entity smallcntr is

elsif clock'event and

port (clock : in std_logic;

clock='1' then

if enb = '1' then

reset : in std_logic;

enb : in std logic;

temp <= temp + 1;

qout : out std_logic_vector

else

(3 downto 0));

temp <= temp;

end smallcntr;

end if;

end if;

architecture arc_cnt of smallcntr is

end process;

signal temp : std_logic_vector

qout <= temp;

(3 downto 0);

end arc_cnt;

begin

```