# 第2章

各社の代表的なデバイスの特徴を知って選択する

# 代表的な各種 CPLD の基礎知識

本章では、CPLDの基本的な動作原理と、代表的な製品シリーズのアーキテクチャと特徴を紹介します、また、代表的な品種を一覧表にまとめたので、デバイスを選択するときの参考になるでしょう。

## 2.1 基本的な構成

### フリップフロップ(レジスタ)

PLDの基本的な構成を知っている方も少なくないと思いますが,念のために簡単に振り返っておきましょう.ロジック回路には**組み合わせ論理回路と順序回路**があり,通常はこれらが混在しています.そして,順序回路の基本的な回路要素は**フリップフロップ**です.値を保持する機能に使われるので**レジス夕**とも呼ばれます.

#### マクロセル

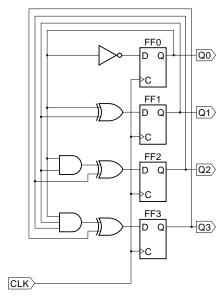

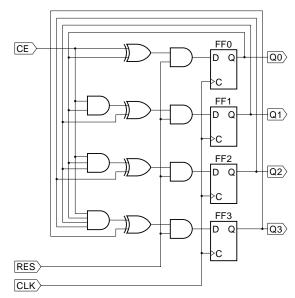

例えばロジック回路でよく使われるカウンタは、レジスタの出力を組み合わせ論理回路でインクリメントしてレジスタの入力に接続するという**図**2.1のような回路構成になっています。もちろん、組み合わせ論理回路にレジスタのフィードバックだけでなく、**図**2.2のように外部入力を接続することもあります。

このように,レジスタとその前段に接続される組み合わせ論理回路のペアがロジック回路の基本的な構成単位になります.そして,PLDではこれを**マクロセル**と呼んでいます.

#### コンピネーション出力

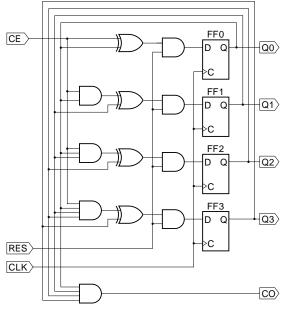

レジスタの出力を組み合わせ論理回路に接続し、そのまま出力したい場合もあります.例えば、カウンタの値をデコードしたいときなどです.このような場合は、**図**2.3に示すようにマクロセルのレジスタをバイパスすることによって実現できます.レジスタをバイパスしたマクロセルの出力は**コンビネーション出力**と呼ばれます.

#### プロダクト・ターム

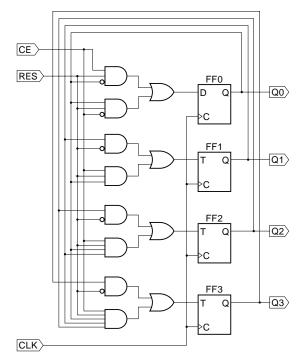

PLDでロジック回路を実現するときは、組み合わせ論理回路の部分は**図**2.2のようにゲートが何段にも接続されることはなく、**図**2.4のように「論理積と論理和だけ」に変換されます.これを**論理圧縮**といいます.論理圧縮はコンパイラが自動的に行ってくれます.この論理積の部分を**プロダクト・ターム**といいます.**図**2.4の回路では、すべてのマクロセルがそれぞれ二つのプロダクト・タームを使っています.

### プロダクト・ターム・アロケータ

一つのマクロセルあたりで使えるプロダクト・タームの数には制限があります.最もシンプルなPLD

図2.1 カウンタ回路の例

図2.2 外部入力信号があるカウンタ

図2.3 デコード出力があるカウンタ

図2.4 図2.2を論理圧縮した回路