強力なビット処理、高速割り込み応答、十分な演算能力、小さなオブジェクト・サイズ

# MCS-51アーキテクチャの概要

## 1-1 MCS-51アーキテクチャの概要

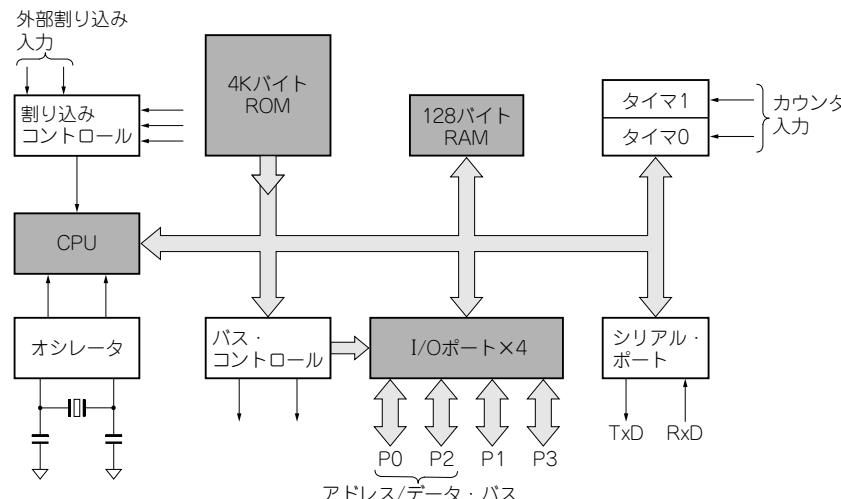

それではいよいよ、8051の説明を始めましょう。図1-1は、元祖であるインテル8051のブロック図です。この図が示すとおり、8051はデバイス単体で動作するマイクロコントローラとして、下記に挙げる機能をすべて内蔵しています。

- CPUコア

- プログラム・メモリ (ROM)

- データ・メモリ (RAM)

- 複数の動作モードをもつ2組の16ビット・タイマ

- 8ビット×4ポートのパラレル・ポート

- 全二重通信が可能なシリアル・ポート

- 割り込みコントローラ

- システム・クロック生成用のクリスタル発振回路

これら8051デバイスがもつ主な機能は、一括して「8051コア」と呼ばれます。

図1-1<sup>(4)</sup> 8051のブロック図

## 1-2 外観とピン・アサイン

オリジナルのパッケージは図1-2のような40ピンDIPです。表1-1は各ピンの簡単な説明です。派生品

見

本

表1-1 各ピンの説明(40ピンDIP)

| ピン番号 | 名 称                      | 説 明                                                                                                    |

|------|--------------------------|--------------------------------------------------------------------------------------------------------|

| 1    | P1.0                     | I/O ポート 1 のビット 0                                                                                       |

| 2    | P1.1                     | I/O ポート 1 のビット 1                                                                                       |

| 3    | P1.2                     | I/O ポート 1 のビット 2                                                                                       |

| 4    | P1.3                     | I/O ポート 1 のビット 3                                                                                       |

| 5    | P1.4                     | I/O ポート 1 のビット 4                                                                                       |

| 6    | P1.5                     | I/O ポート 1 のビット 5                                                                                       |

| 7    | P1.6                     | I/O ポート 1 のビット 6                                                                                       |

| 8    | P1.7                     | I/O ポート 1 のビット 7                                                                                       |

| 9    | RST                      | リセット入力                                                                                                 |

| 10   | P3.0/RXD                 | I/O ポート 3 のビット 0 またはシリアル入力ポート                                                                          |

| 11   | P3.1/TXD                 | I/O ポート 3 のビット 1 またはシリアル出力ポート                                                                          |

| 12   | P3.2/ <u>INT0</u>        | I/O ポート 3 のビット 2 または外部割り込み 0                                                                           |

| 13   | P3.3/ <u>INT1</u>        | I/O ポート 3 のビット 3 または外部割り込み 1                                                                           |

| 14   | P3.4/T0                  | I/O ポート 3 のビット 4 またはタイマ / カウンタ 0 外部入力                                                                  |

| 15   | P3.5/T1                  | I/O ポート 3 のビット 5 またはタイマ / カウンタ 1 外部入力                                                                  |

| 16   | P3.6/ <u>WR</u>          | I/O ポート 3 のビット 6 または外部メモリ・ライト・ストローブ                                                                    |

| 17   | P3.7/ <u>RD</u>          | I/O ポート 3 のビット 7 または外部メモリ・リード・ストローブ                                                                    |

| 18   | XTAL2                    | インバータ発振回路の出力                                                                                           |

| 19   | XTAL1                    | インバータ発振回路の入力                                                                                           |

| 20   | <u>V<sub>SS</sub></u>    | グラウンド                                                                                                  |

| 21   | P2.0/A8                  | I/O ポート 2 のビット 0 またはアドレス・バスのビット 8                                                                      |

| 22   | P2.1/A9                  | I/O ポート 2 のビット 1 またはアドレス・バスのビット 9                                                                      |

| 23   | P2.2/A10                 | I/O ポート 2 のビット 2 またはアドレス・バスのビット 10                                                                     |

| 24   | P2.3/A11                 | I/O ポート 2 のビット 3 またはアドレス・バスのビット 11                                                                     |

| 25   | P2.4/A12                 | I/O ポート 2 のビット 4 またはアドレス・バスのビット 12                                                                     |

| 26   | P2.5/A13                 | I/O ポート 2 のビット 5 またはアドレス・バスのビット 13                                                                     |

| 27   | P2.6/A14                 | I/O ポート 2 のビット 6 またはアドレス・バスのビット 14                                                                     |

| 28   | P2.7/A15                 | I/O ポート 2 のビット 7 またはアドレス・バスのビット 15                                                                     |

| 29   | <u>PSEN</u>              | プログラム・ストア・イネーブル。外部プログラム・メモリのリード・ストローブ。                                                                 |

| 30   | <u>PROG/ALE</u>          | アドレス・ラッチ・イネーブル。外部メモリ・アクセス中にアドレスの下位バイトをラッチするためのパルス出力。EPROM デバイスではプログラム・パルス入力。                           |

| 31   | <u>V<sub>DD</sub>/EA</u> | 外部アクセス・イネーブル。内部プログラムを実行するときは <u>V<sub>CC</sub></u> 、外部プログラムを実行するときは <u>V<sub>SS</sub></u> へそれぞれ接続すること。 |

| 32   | P0.7/AD7                 | I/O ポート 0 のビット 7 または外部メモリ・アクセス中の下位バイト・アドレス / データ・ビット 7                                                 |

| 33   | P0.6/AD6                 | I/O ポート 0 のビット 6 または外部メモリ・アクセス中の下位バイト・アドレス / データ・ビット 6                                                 |

| 34   | P0.5/AD5                 | I/O ポート 0 のビット 5 または外部メモリ・アクセス中の下位バイト・アドレス / データ・ビット 5                                                 |

| 35   | P0.4/AD4                 | I/O ポート 0 のビット 4 または外部メモリ・アクセス中の下位バイト・アドレス / データ・ビット 4                                                 |

| 36   | P0.3/AD3                 | I/O ポート 0 のビット 3 または外部メモリ・アクセス中の下位バイト・アドレス / データ・ビット 3                                                 |

| 37   | P0.2/AD2                 | I/O ポート 0 のビット 2 または外部メモリ・アクセス中の下位バイト・アドレス / データ・ビット 2                                                 |

| 38   | P0.1/AD1                 | I/O ポート 0 のビット 1 または外部メモリ・アクセス中の下位バイト・アドレス / データ・ビット 1                                                 |

| 39   | P0.0/AD0                 | I/O ポート 0 のビット 0 または外部メモリ・アクセス中の下位バイト・アドレス / データ・ビット 0                                                 |

| 40   | <u>V<sub>CC</sub></u>    | 電源入力                                                                                                   |