## 第5章

# 専用ハードウェアを使わずにI<sup>2</sup>CのEEPROMにアクセスする ソフトウェア制御によるI<sup>2</sup>Cマスタ(PIC/H8)

この章では、PIC/H8ボードをマスタとして、 $I^2$ C EEPROMへアクセスできるソフトウェアを作成して動作を確認します、 $I^2$ C EEPROMには手軽な24LC64(64Kビット)を使います。

### 5-1 ソフトウェアによるI<sup>2</sup>Cマスタ

#### ● 実験環境

第4章または第5章で製作したマイコン・ボードに、ここで製作するI<sup>2</sup>C EEPROMのサブ・ボードを接続して、ソフトウェア駆動のドライバによりEEPROMを制御します。機器構成とバス信号の接続は、図 5-1のようになります。

#### ● ソフトウェア制御について

専用ハードウェアを使わない場合、I<sup>2</sup>Cのタイミングをソフトウェアで作らなければならないため、正確な周期のシリアル・クロックSCLは生成できません。しかし、同期式通信の特徴としてクロックが動作の基準となるため、SCLとシリアル・データSDAの変化タイミングが適正な関係を満たしている限り通信には問題ありません。MSSPなどの専用ハードウェアがなくても、アクセス・タイムが遅くなるなどの

図5-1

EEPROMアクセスの実験機材の構成マスタ機にスレーブ・デバイスのEEPROMを接続して読み書きを確認する実験のときの使用機材の構成を示す。EEPROMのI<sup>2</sup>Cアドレスはハードウェア的に'0'に固定している。

制限は付きますが、I<sup>2</sup>CタイプのEEPROMなどを使うことができます。

また、今回作成するプログラムでは、クロック・ストレッチの機能はサポートしていません。EEP-ROMなどのハードウェアのI<sup>2</sup>Cスレーブを接続する場合は、スレーブ側がマスタに比べて十分に高速のため問題はありませんが、第8章で解説するソフトウェア制御のスレーブ・デバイスを接続した場合は、マスタの速度にスレーブ側の処理が追いつかずに通信できない場合があります。この場合は、通信するバイトごとに十分なインターバル時間を設けて間欠的にデータを送受信するなど、マスタ側にも対策が必要になります。

#### ● I<sup>2</sup>Cマスタ・ドライバ

ここでは、 $I^2$ C通信を制御する上で使用する基本的なルーチンをいくつか作ります。これらのルーチンをドライバと呼びます。今回作成するドライバには、 $I^2$ C関係の初期化ルーチン、スタート・コンディション、ストップ・コンディションの発生ルーチン、1バイト・データの読み/書きルーチンなどがあります。

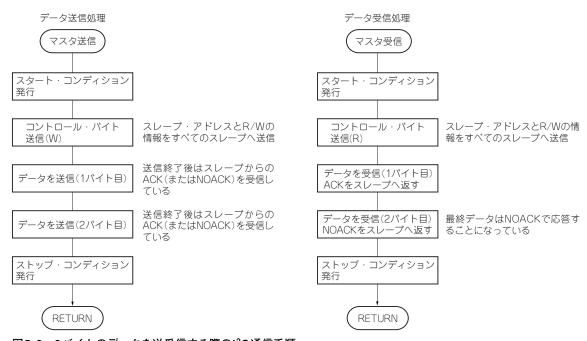

処理の詳細は図5-2(pp.74~75)のフローチャートに示しますが、マスタ側のプログラムは比較的簡単です。SCLとSDAの切り替わりの順序に気を付けるのと、セットアップ・タイム(安定時間)が確保できていることが重要ですが、それ以外は1ビットのデータをSCLを切り替えながら8ビット分入出力し、9ビット目にACKデータを出力または入力するというようなものになります。データ・ビット、ACKビットの入出力は、SCLの立ち上がりエッジに行われます。ドライバの一覧はAppendix-C にまとめてあります。サブルーチン名は次章のハードウェア制御のドライバ・ルーチンと同じ名前にしてあるので、ハードウェア制御かソフトウェア制御かはリンクするオブジェクト・ファイルで切り替えます。

$I^2$ Cの入出力の一般形として、2バイトのデータをマスタが読み書きする場合のフローチャートを $\mathbf{Z}$ 5-3

図5-3 2バイトのデータを送受信する際のI<sup>2</sup>C通信手順マスタがスレーブに2バイトのデータを送受信する際の一般的な処理手順を示すフローチャート.