# 第5章

### 高速・低電圧動作 最新 FPGA の電源要求に応える

## 高速応答 POL コンバータの 開発から学ぶ

## 鈴木 正太郎

Syotaro Suzuki

最新ディジタル・システムの要としてFPGAの利用が一般的になってきました。しかし、FPGA自身は常に最新半導体プロセスを追いかける宿命をもっており、微細化=高速化と低電圧化が表裏関係です。結果、改めて注目されているのが最新FPGAへの電源配給技術とプリント基板への実装技術です。そして、電源配給担当であるPOLにも(0A→6.5 A/160 ns)という高速負荷応答力が求められるようになってきました。

### 最新デバイス FPGAが電源に求めるもの

### ● 一般化してきた FPGA の利用

FPGA(フィールド・プログラマブル・ゲート・アレイ)は、プログラミングにより回路を再構成できるので短期間でハードウェアの変更をしなくてもプログラムの変更でシステムの変更ができ、製品の開発期間を短縮することができます。

これらの利便性から FPGA は ASIC を置き換えるディジタル・システムの有望なソリューションとなり、急速に市場を拡大させてきました。また LSI …半導体の微細化技術の進展と共に、市場ニーズに適応した高

性能,低価格FPGAの登場でますます利用が高まっています.

半導体プロセスの微細化技術の進展は目覚しく、2006年にリリースされた米 Xilinx 社、米 Altera 社の最新 FPGA の回路パターン幅は 60 nm となり、超微細化時代となりました。

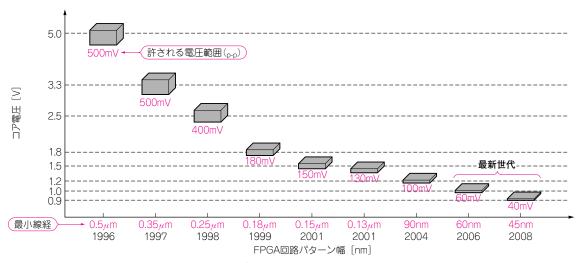

図1はFPGAのプロセスの進化と回路パターン幅の推移を図にしたものですが、設計パターン幅の微細化に伴い、コア…内部素子の動作電圧の低電圧化も著しく進んでいることがわかります。

一方,技術的問題も生じてきました。FPGAの超微細化でパターン幅が60 nmになったことでコア電圧は低電圧となり,この低電圧化がFPGA 駆動電源の許容電圧値も極端に低くさせ,これが要因でFPGAが電源障害を起こすことが懸念されています。低電圧駆動が要因で電源障害を起こす現象はパターン幅90 nm,コア電圧1.5 VタイプのFPGAでも数多く報告されていて,60 nm,さらに45 nmとなると,想像以上のトラブルが予想されます.

ここでは低電圧駆動のICとしてFPGAを例に解説しますが、内容はFPGAでもMPUでもASICでも同

〈図1〉FPGAのプロセス進化とICコア電圧の許容範囲

じ問題を内包します. FPGA = 低電圧動作のICとして読み直しながら理解を深めてください.

#### 微細化と電源障害の問題

最新の FPGA を駆動する電源電圧は、高密度化する素子数や駆動速度に反比例し低電圧化され、コア電圧は $2.5 \text{ V} \rightarrow 1.8 \text{ V} \rightarrow 1.5 \text{ V} \rightarrow 1.3 \text{ V} \rightarrow 1.2 \text{ V}$  とどんどん低くなっています。つまり最新のハイエンド FPGAのコア電圧は急速に低電圧化が進み、電流は大電流化してきました。さらに FPGA を搭載するプリント基板も高密度実装化され、多層プリント基板での電源配線と電源の実装は、従来にまして複雑で面倒な問題として浮上しています。

図1にはFPGAのプロセスの進化とICのコア電圧の許容範囲値も示しています。たとえばコア電圧が3.3 V の場合のコア電圧許容範囲は500 mV $_{p-p}$ で、これならあまり問題にならないオーダです。しかし、パターン幅90 nmでのコア電圧許容範囲は100 mV $_{p-p}$ となっています。100 mV というと、電源負荷急変時の電圧変動だけでこの値を超えてしまい、FPGA が誤動作を起す危険性が高まります。

このように、微細化された半導体プロセスの恩恵と 現実は、

- (1) より高密度実装が可能になる

- (2) 微細化で内部コアの更なる高速動作が実現した

- (3) 高実装密度化で低コストを実現した

また、微細化したプロセスの現実は、回路動作が高 速化された結果、

- (1) 大電流化(消費電力が上がる)が生じる

- (2) 電源障害やグラウンドのバウンズ問題が発生

- (3) ノイズ対策に費やす時間費用が増加する

- (4) 消費電力はほぼ同等か上昇傾向となる

(5) プリント・パターン設計や実装設計がより困難 になりました。

しかも、半導体の微細化は消費電力を増加させました。90 nmプロセスの場合、

- (1) 130 nm に比べてトランジスタの数が2倍になった

- (2) 素子のスイッチング周波数がより高速化した

- (3) 素子数の増加でジャンクション容量が増加した

- (4) 抵抗性負荷ロス低減のために銅プロセスが導入 された,

- (5) リーク電流が増加した

という状況を作り、トータルではますます低電圧・大 電流化へと進化しています.

### ● 従来はプリント基板の端に DC-DC コンバータ配置

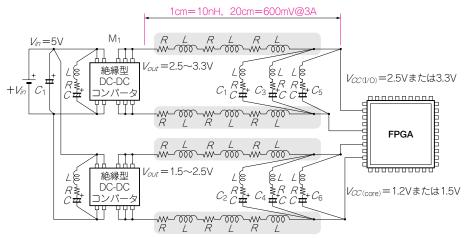

同じプリント基板上に電源と負荷回路を実装する場合,これまでDC-DCコンバータは電源の入り口である入力端子付近(基板の縁)に配置していました(図2).

なぜ、このような実装配置が常識であったのか?

理由は、DC-DCコンバータがスイッチング動作によってノイズを発生するので、プリント基板の端に配置してノイズの影響を防ぐために実施されてきたのです。これまでのディジタル回路は5Vまたは3.3V電源が使われるのが普通でした。

図2は、これまで一般的に使用されているプリント基板上のDC-DCコンバータと、負荷であるIC間の配置イメージ図です。DC-DCコンバータは前記の理由でコネクタ端子近くに配置され、電源の出力はプリント配線によって負荷であるディジタルIC…FPGAまで電源を給電されています。

この場合,電源と負荷間はプリント配線距離が長く,

〈図2〉 DC-DCコンバータを基板 の端に配置すると