## コンピュータ・システム 山武 一朗

## M32R ソフト・コアの FPGA への実装事例 筆8回

今回は,前回紹介した M32R ソフト・コア(ルネサス テクノ ロジ製)を,実際にFPGAに実装する場合の具体的手順につい て解説します.

## M32R ソフト・コアの組み込み手順

EDK は使えない?!

連載第2回から第6回で解説したソフト・コア(ソフト CPU コアともいう)MicroBlazeは, EDKという設計ツールを使うこ とで簡単に Xilinx 社製の FPGA に組み込むことができました. しかし,特定のベンダのデバイスや設計ツールに依存しない汎 用ソフト・コアの場合は, どのようにして FPGA に実装するの でしょうか.

本キットに添付予定の M32R ソフト・コアも, 基本的には特 定のデバイスや設計ツールに依存しない、汎用のソフト・コア です[ただし,実際には本キットに添付の M32R ソフト・コア 評価版は,本キットに実装している FPGA 専用(Spar tan3/1500)に設計されている〕.

ソフト・コアといっても,何も特別なツールが必要なわけで はありません. Xilinx 社製デバイスの場合は設計ツール ISE を 使って,ユーザ回路といっしょに論理合成&配置配線を行い, 最終的にビット・ストリーム・ファイルを作成します. もちろ ん,無償で使える設計ツール ISE WebPACK でも, M32R ソフ ト・コアを組み込むことができます.

IP コアのファイル提供の方法

IP コアのファイル提供方法には,一般的に次の二つの方法が あります.

- (1) HDL ソース提供

- (2)ネット・リスト提供

本キット添付の M32R ソフト・コアは,後者のネット・リス トで提供されています、そのため CPU コアの中身を改造して カスタマイズすることはできませんが, CPU コアのバスに周辺 機能を接続して、一つのデバイスに実装することが可能になっ ています. つまり, ユーザの手元で SoC(System On Chip)を 実際に設計し,動作させてみることができるのです.

なお, Xilinx 社製デバイスで扱うネット・リスト形式は,拡

張子がngcというファイルになります.

## M32Rソフト・コア・モジュールの 2 1/0 信号の設定

2種類のネット・リスト

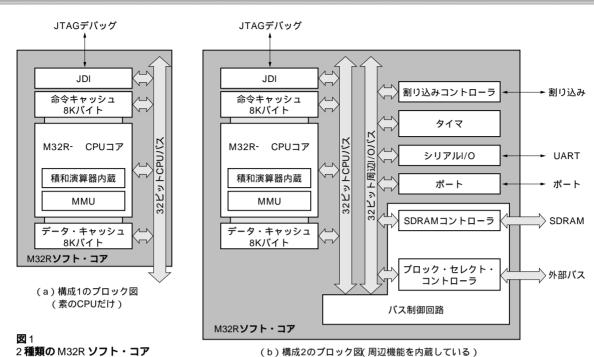

前回解説があったように,本キットに添付される M32R ソフ ト・コアのネット・リストは、図1に示すような2種類の構成 があります.

構成1は,CPUコアとキャッシュ,JTAGデバッグ・モ ジュールなど,いわゆる素の CPU だけのモジュールで,ネッ ト・リストの I/O 信号としては, M32R コアの生のバスが直接 出ているタイプです、CPU コアにはキャッシュも内蔵されてい るので、キャッシュ・フィル時はメモリのバースト・リード・ アクセスが, ライト・バック時にはバースト・ライト・アクセ スが発生します.この M32R の生のバスを直接扱うには, CPU コアの動作に関する深い理解が必要で,このバスにユーザ回路 を接続するのはちょっと難易度が高そうです.

もう一つの構成2は,構成1に追加して,割り込みコント ローラやタイマ、シリアル、ポート、SDRAM コントローラや ブロック・セレクト・コントローラと呼ばれる外部バス・コン トローラまでが内蔵されたものです、こちらのネット・リスト の I/O 信号には, それぞれのコントローラが外部と通信するた めの信号が出ています. SDRAM コントローラからは SDRAM を接続するための信号が直接出ているので、何も考えずに対応 する信号を SDRAM の各信号ピンと接続するだけで, SDRAM を問題なく読み書きすることができます.また,ブロック・セ レクト・コントローラから出てくる外部バス信号も,一般的な 組み込み向け CPU のローカル・バスと同様です.こちらのネッ ト・リストを使ったほうが,簡単にユーザ回路を接続できそう

構成2のネット・リストを使う理由

以上のような理由から,今回は構成2のネット・リストを使 うことにします.これにはもう一つ理由があります.

一般的に M32R のプログラムは SDRAM 上に格納します.こ こで構成1のネット・リストを使った場合は,SDRAM コント ローラも自前で用意する必要があります.また,SDRAMコン

表 1 構成 2 の CPU コア・モジュールの I/O 信号一覧 —

| 信号名                    | 入出力 | 名 称               |

|------------------------|-----|-------------------|

| CXXIN                  | 入力  | システム・クロック         |

| CXRESET                | 入力  | システム・リセット         |

| CXBCLK                 | 出力  | バス・クロック           |

| CXRD0 ~ 31             | 入力  | リード・データ・バス        |

| CXWD0 ~ 31             | 出力  | ライト・データ・バス        |

| CXWDAT_OEN             | 出力  | ライト・データ・バス出力イネーブル |

| CXBSEL0 ~ 7            | 出力  | ブロック・セレクト         |

| CXROMSZ                | 入力  | BSEL0バス幅          |

| CXA6~30 <sup>注</sup>   | 出力  | アドレス・バス           |

| CXWS0 ~ 3 <sup>注</sup> | 出力  | ライト・ストローブ         |

| CXRS                   | 出力  | リード・ストローブ         |

| CXREADY                | 入力  | レディ               |

注:正確にはCXA30とCXWS2は1本の信号で,データ・バス幅が32ビットの時はCXWS2として,16ビットの時はCXA30として動作する(排他動作)

(a)外部バス系信号

| 信号名   | 入出力 | 名 称     |

|-------|-----|---------|

| CXTXD | 出力  | 送信データ   |

| CXRXD | 入力  | 受信データ   |

| CXRTS | 出力  | フロー制御出力 |

| CXCTS | 入力  | フロー制御入力 |

(c) UART 系信号

トローラそのものは十分に信頼のおける IP コアを使ったとしても、それを M32R コアと接続する部分は、だれかが記述しなければなりません.ここでもし、CPU と SDRAM の間の接続に問題があり、CPU が正常にメモリをアクセスできない場合は、たとえプログラムと接続したユーザ回路は正しくても、システムとして正常な動作は望めず、原因の究明が難しくなります.

構成2を使うとSDRAM コントローラまで含まれているので,

| 信号名            | 入出力 | 名 称               |

|----------------|-----|-------------------|

| CXSDCLK        | 出力  | SDRAM 駆動用クロック     |

| CXDCKE         | 出力  | クロック・イネーブル        |

| CXBA           | 出力  | バンク・アドレス          |

| CXMA12 ~ 0     | 出力  | アドレス・バス           |

| CXDQM3 ~ 0     | 出力  | データ出力マスク          |

| CXDCS1 ~ 0     | 出力  | チップ・セレクト          |

| CXDRAS         | 出力  | RAS               |

| CXDCAS         | 出力  | CAS               |

| CXDWE          | 出力  | WE                |

| CXSDRDAT31 ~ 0 | 入力  | リード・データ・バス        |

| CXSDWDAT31 ~ 0 | 出力  | ライト・データ・バス        |

| CXSDWDAT_OEN   | 出力  | ライト・データ・バス出力イネーブル |

(b) SDRAM 系信号

| 信号名    | 入出力 | 名 称  |

|--------|-----|------|

| CXTCK  | 入力  | TCK  |

| CXTRST | 入力  | TRST |

| CXTMS  | 入力  | TMS  |

| CXTDI  | 入力  | TDI  |

| CXTDO  | 出力  | TDO  |

| CXDBI  | 入力  | DBI  |

(d)JTAG デバッグ系信号

| 信号名           | 入出力 | 名 称          |

|---------------|-----|--------------|

| CXPx_OUT0 ~ 7 | 出力  | ポート出力信号      |

| CXPx_IN0 ~ 7  | 入力  | ポート入力信号      |

| CXPx_OEN0 ~ 7 | 出力  | ポート出力イネーブル信号 |

注: x はポート番号で, 0 ~ 9まで合計 80 ビット分 (e) ポート系信号

| 信号名        | 入出力 | 名 称           |

|------------|-----|---------------|

| CXSBI      | 入力  | システム・ブレーク割り込み |

| CXINT0 ~ 7 | 入力  | 外部割り込み入力      |

(f)割り込み系信号

Interface Sept. 2006