# ARMアーキテクチャの 基礎知識

中森 章

特集を始めるにあたり、まずはARMプロセッサとはどのようなCPUアーキテクチャなのかを詳しく解説する。ARMプロセッサにはいくつかのアーキテクチャとCPUコアの種類がある。また、ほとんどの命令に実行する/しないを決める条件フラグが付いていたり、ロード/ストア命令に豊富なアドレッシング・モードがあるなど、ARMアーキテクチャの特徴的な命令セットについても解説する。

(編集部)

# 1. ARMとは

ARM は会社の名称であるとともに, ARM 社が設計し, ライセンス供給を行っているプロセッサの総称でもあります. 命令セット・アーキテクチャ, それを実装する CPU コア, CPU コアにキャッシュ, MMU(メモリ管理ユニット), バス・インターフェースなどを付加したプロセッサ IP, プロセッサ IP と周辺回路を集積した ARM アーキテクチャの半導体チップを指します.

ARM 社のプロセッサは, Intel 社や AMD 社などの CPU メーカとは異なり, 単体のチップがそのまま発売されることはまずありません. ARM 社から IP(設計情報)の提供を受けた半導体企業(シリコン・パートナ)が, それを使って独自の機能や技術を加えて, 汎用マイクロプロセッサや ASIC, ASSP などの SoC

# COLUMN<mark>1</mark> ASIC、ASSP、ASCPの違い

コラムのタイトルにある英文字の略語,これらはすべてシステム LSI の構成を表すことばです.ASIC(Application Specific Integrated Circuit)とは特定用途向けの IC のことです.しかし,その定義はあいまいなまま使用されることが多くあります.ASIC を広義に解釈すると,特定用途向けに特化した機能を有する IC のすべてを含みます.つまり,ASSP(Application Specific Standard Product)や ASCP(Application Specific Customer Product)も ASIC の一部です.ASSPとは特定用途向けの標準品,ASCPとは特定用途向けのカスタム・チップです.ASSPと ASCPの違いは一般売りをするか否かの違いでしかありません.また,狭義では,ASICは顧客の要求を受けて開発する専用 IC を指すことが一般的です.ゲートアレイ製品やPLD(Programmable Logic Device)がその代表です.その意味で,ASCPと ASIC は同一視されることが多々あります.

(System on a Chip)を開発・販売します.これが,携帯電話やディジタル家電のアプリケーション・プロセッサとして広く使用されています.

よって、読者の方々が ARM プロセッサを使ってシステムを 開発しようと思い、CPU を買うために ARM 社に問い合わせて も、デバイスは売ってもらえません、ARM 社からライセンス を受けた各半導体ベンダの中から、汎用品として市販されてい るデバイスを購入するか、いずれかのベンダに ASIC 開発を依 頼することになります。

本特集では前者のパターンを想定し,第2章から第6章のそれぞれで,半導体ベンダが汎用品として市販している CPU を取り上げ,その使いかたを解説しています.

# 2. ARMプロセッサのアーキテクチャ概要

## ARM アーキテクチャの変遷

ARM プロセッサの基本的なアーキテクチャや命令セットは,初期のものからほとんど変更されていません.しかし,ARMアーキテクチャと命令セットは,もともと1980年代中頃に開発されたため,現在や将来の組み込みシステムに必要な機能(16ビット・モードやJavaアクセラレータなど)が何世代にも渡って追加されてきました.

ARM ではアーキテクチャのバージョンを示すのに, v4 や v5 と表現します. さらに" T "は Thumb, " E "は DSP 拡張 ( Enhanced DSP ), " J "は Java 拡張( Jazelle )の機能を示し, v4T とか v5TEJ などと表示します. また, TrustZone を内蔵する v6Z や Thumb-2 を内蔵する v6T2 というアーキテクチャもあります. なお現在では, v4T 以降のアーキテクチャのみが有効です.

さらに ARM では、CPU コアに番号を付けて呼んでいます. ARM1 ~ 3 は ARM 社設立以前に前身の Acorn 社で設計されたコアで、ARM 社設立後最初に設計されたコアが ARM6 です(4 と5 は番号が飛ばされた). そして ARM6 の後継として開発さ

# ARM アーキテクチャの 基礎知識

#### 表 1 ARM アーキテクチャの変遷

| v1    | 最初の命令セット.ほとんど使用されていない                                |  |

|-------|------------------------------------------------------|--|

| v2    | 乗算命令とコプロセッサをサポート                                     |  |

| v2a   | キャッシュのサポートと同期命令( SWP )の追加                            |  |

| v3    | ARM 社独立後の最初のアーキテクチャ                                  |  |

| v3G   | 詳細不明 . v2a と互換性なし                                    |  |

| v3M   | 結果が64 ビットの乗算                                         |  |

| v4    | システム・モードのサポート.アーキテクチャの完成版                            |  |

| v4T   | Thumb モードの追加                                         |  |

| v5T   | BLX , CLZ , BKPT 命令の追加                               |  |

| v5TE  | DSP 命令セットの追加                                         |  |

| v5TEJ | Java 拡張( Jazelle )の追加                                |  |

| v6    | マルチメディア拡張(SIMD).<br>同期命令の強化(LDREX/STREX). 割り込み応答の高速化 |  |

| v6T2  | Thumb-2 モードの追加                                       |  |

| v6Z   | TrustZone の追加                                        |  |

| v7    | 最新アーキテクチャ(詳細は第7章を参照)                                 |  |

#### (a) アーキテクチャ

| ARM1 ~ 3 | Acorn 社時代に設計されたコア<br>(現在は使われていない)    |  |  |

|----------|--------------------------------------|--|--|

| ARM4 ~ 5 | 存在しない                                |  |  |

| ARM6     | ARM 社として最初に設計されたコア<br>( 現在は使われていない ) |  |  |

| ARM7     | 現在の ARM プロセッサの基本コア                   |  |  |

| ARM8     | (現在は使われていない)                         |  |  |

| ARM9     | 5段パイプラインへ拡張                          |  |  |

| ARM10    | 6段パイプラインへ拡張                          |  |  |

| ARM11    | 8段パイプラインへ拡張                          |  |  |

(b) コア・ファミリ

れたのが, 現在の ARM の基本コアともいえる ARM7 です.以 降,コアの性能向上を目指し,新しいバージョンのコアが設計 されています.

コアとアーキテクチャの対応は,基本的に次のようになって います. ARM6と前期の ARM7がv3,後期の ARM7~ ARM9 が v4, ARM10 が v5, ARM11 が v6 です. ARM7 も最新の Rev.4 では Thumb を内蔵し v4T になっています. 流れとして は新しいバージョンのコアほど,新しいバージョンのアーキテ クチャが使われています.ただし一部には,ARM7やARM9 のコアでも v5 アーキテクチャを採用している CPU もあります.

# 表1に ARM アーキテクチャの変遷を示します.

## ARM アーキテクチャの実装

最初の ARM アーキテクチャのプロセッサが開発された当時, RISC はStanford University の MIPS と, University of California, Berkeley (UC-Berkeley )の RISC , (SPARC の母体 )しか 例がありませんでした. ARM が Berkeley RISC を参考にして 設計されたのは周知の事実です.設計目標は, CISC ライクな 命令セットを, RISC に準じた単純なハードウェアで実行する ことに置いています.その基本はパイプライン処理です.

ARM のCPU コアでは, ARM1 ~ 7, ARM9(ARM8), ARM 10, ARM11 でパイプラインの構成に若干の差異があります.

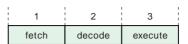

(a)一般命令のパイプライン

| 1     | 2      | 3          | 4         | 5         |

|-------|--------|------------|-----------|-----------|

| fetch | decode | calc.addr. | date xfer | reg.write |

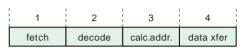

(b) ロード命令のパイプライン

(c) ストア命令のパイプライン

#### 図1 ARM7 のパイプライン構成

## 表2 パイプライン・ステージの意味

| fetch       | 命令フェッチ   | メモリから命令をフェッチし,パイ<br>プラインに投入する                                                      |

|-------------|----------|------------------------------------------------------------------------------------|

| decode      | 命令デコード   | 命令をデコードし,データパスの制<br>御信号を生成する                                                       |

| execute     | 実行       | 命令のデコード結果に従い,レジスタ・ファイルをリードし,オペランドを(必要なら)シフトし,演算を行い,結果をレジスタにライトする                   |

| calc. addr. | アドレス計算   | ロード/ストア/分岐命令の場合は演算器を用いてオペランドまたは分岐<br>先のアドレスを計算する.ストア命令ではさらにメモリにストアするレ<br>ジスタをリードする |

| data xfer   | データ転送    | ロード命令ではメモリからオペランド・データをリードする.ストア命令ではレジスタの値をメモリにライトする                                |

| reg. write  | レジスタ・ライト | ロード命令でメモリからリードした<br>データをレジスタにライトする                                                 |

それぞれのコアの特徴とパイプラインを簡単に見ていきましょ う.

## ▶ ARM7 コアの特徴

ARM7は,コアの実装面積が小さいため,コストと消費電力 が重視されるアプリケーション分野を対象にしています. 近年 では Thumb 命令セットをサポートするようになり, コード・ サイズが重視される分野における採用も期待されています.

図 1(a)に ARM1 ~ ARM7 のパイプラインを示します. その 基本は単純な3ステージ構成のパイプラインです.ただし,ロー ド/ストア/分岐命令などはマルチサイクル命令として別のパイ プライン処理を行います. それを図1(b)と図1(c)に示します. 表2に各パイプライン・ステージの意味を示します.

## ▶ ARM9(ARM8)コアの特徴

ARM9 コアは,中~高性能レンジの CPU コア製品群です. ARM9製品はすべて Thumb 命令セットを搭載したカスタム設 計のハード・マクロセルです、論理合成可能なコアとしては ARM9E があります. ARM9E では, Thumb および ARM DSP