# 組み込みシステム 開発評価キット 活用通信

第 5 回 ■ BLANCA システム・バスと IDE&CompactFlash へのブリッ

BLANCA システム・バスはデータ・バス幅 32 ビットのバスです.組み込みシステム開発評価キットには,IDE や Compact Flash といった 16 ビット・バスのインターフェースも実装されています.今回は,BLANCA システム・バスからこれら 16 ビット・バス系のインターフェースへのブリッジ方法について解説します.

# 1.CPU 外部バスと BLANCA システム・バスのブリッジ

アドレス・バスの下位ビットとバイト・イネーブル BLANCA システム・バスのアドレス・バスは , MSB 側の A31 から LSB 側の A0 まで , 32 本が用意されています . しか し , すべてのプラットホームにおいて , 32 本のアドレス・バス が有効かというと , そうでない場合もあります .

表1に,現在,本評価ボードで使用可能なCPUコアが持つ外部バス信号についてまとめました.さらに現在開発中のオプションCPUカードSH-4Aの外部バス信号についても併せて掲載しました.

#### MicroBlaze の場合

CPU コアとして MicroBlaze を使う場合は , アドレス・バス 32 本すべてが有効となります . また , データ・バス 32 ビット中 , どのバイトの位置に対してのアクセスなのかを示すバイト・イネーブル情報も , リード/ライト信号とは独立して用意されています . これにより , バイト単位のアドレスにバイト・サイズでアクセスした場合でも , そのアドレスもデータ・バス中のバイト位置も , すべて外部回路が正しく把握できます . 表 2 に各種アドレスおよびサイズでアクセスした場合のアドレス・バスとバイト・イネーブル情報の例を示します .

なお,表1(a)や表2の MicroBlaze の外部バスの信号は,実際には MicroBlaze のバスの信号名ではありません.『コンピュータ・システム技術学習キット活用通信』の第4回(本誌2006年5月号,pp.173-184 がMicroBlaze にユーザ回路を接続する方法」でも解説したように,BLANCAシステム・バスへはIPIF機能を使ってブリッジしています.そのため,表1(a)にはIPIF機能の信号名を表記しています.

ちなみに, MicroBlaze はビットの並びをビッグ・エンディアンで表記するため, アドレス・バスやデータ・バスの MSB がA0/D0, LSB がA31/D31 となります.

#### M32R ソフト・コアの場合

M32R ソフト・コアも MicroBlaze と同じように,ビット並びをビッグ・エンディアンで表記します.

『コンピュータ・システム技術学習キット活用通信』第7回~第9回(本誌 2006年8月号~10月号掲載)で解説したように,M32R ソフト・コアの外部バス・コントローラが管理する物理アドレス空間は512M バイトしかありません.この全512M バイトの空間を64M バイトごとのエリアに分割して管理し,それぞれのエリアは8本のブロック・セレクト信号で選択されます.したがって,外部バス・コントローラから出力されるブロック・セレクト信号は8本,アドレス・バスの MSB は A6 となります.

アドレス・バスは LSB 側についても注意が必要です.データ・バス幅が 32 ビットのときは A29 まで,16 ビットの時は A30 までしか出力されていません.これは,データ・バス幅を 32 ビットに設定した場合は,1ワード 32 ビットの空間が必要なときであり,ワード単位でアドレッシングできれば,それより 細かいバイト単位でのアドレッシング情報は不要という考えで設計されていることを意味します.コンピュータ・システムとして,この考え方は非常に合理的です.

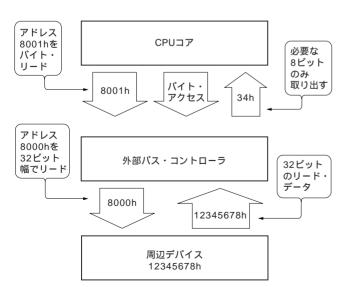

しかし、CPU コアとすればバイト単位のアドレッシングも可能です.CPU コアがバイト単位でリード・アクセスした場合の動作を図1に示します.外部バス・コントローラとしては32ビット幅での読み出し動作となり、周辺回路は32ビット幅でデータを返します.CPU コアは、その32ビット幅の中から実際にアクセスしたいバイト位置のデータだけを取り出すわけです.

リード時は32 ビット幅で読み出して不要なデータは読み捨てればよいのですが,ライト時はそうはいきません.そのためライト時のみ,ライト・バイト・イネーブルとして32 ビット中,どのバイトの位置を書き換えるかの情報が出力されるわけです.

以上のような仕様の M32R ソフト・コアの外部バス・コント ローラから, BLANCA システム・バスへのブリッジ回路では, アドレス・バス A28 ~ A26 は8本のブロック・セレクト信号を

#### 表1 CPU 外部バス信号一覧

| チップ・セレクト   | Bus2IP_ArCS(0)               |

|------------|------------------------------|

| アドレス・バス    | Bus2IP_Addr( A0 ~ A31 )      |

| リード・データ・バス | IP2Bus_ArData( D0 ~ D31 )    |

| ライト・データ・バス | Bus2IP_ArData( D0 ~ D31 )    |

| リード/ライト    | Bus2IP_RNW                   |

|            | (" H " : リード , " L " : ライト ) |

| バイト・イネーブル  | Bus2IP_ArBE(0 ~ 3)           |

| アクノリッジ     | IP2Bus_Ack                   |

(a) MicroBlaze(IPIF経由)

|                   | データ・バス                |          |  |  |  |

|-------------------|-----------------------|----------|--|--|--|

|                   | 32 ビット                | 16 ビット   |  |  |  |

| チップ・セレクト          | <del>CS</del> (6 ~ 0) |          |  |  |  |

| アドレス・バス           | A(25 ~ 0)             |          |  |  |  |

| データ・バス            | D(31 ~ 0) D(15 ~ 0)   |          |  |  |  |

| リード/ライト           | R/W(" H ": リード ,      | "L":ライト) |  |  |  |

| リード               | RD                    |          |  |  |  |

| ライト・バイト・<br>イネーブル | WE(3 ~ 0)             | WE(1~0)  |  |  |  |

| レディ               | RDY                   |          |  |  |  |

(c) SH-4A(SH-3/4/4A)の標準バス・モード時

|                   | データ・バス                              |                  |  |  |  |

|-------------------|-------------------------------------|------------------|--|--|--|

|                   | 32 ビット                              | 16 ビット           |  |  |  |

| ブロック・セレクト         | CXBSEL(0~7)                         |                  |  |  |  |

| アドレス・バス           | CXA( A6 ~ A29)                      | CXA(A6 ~ A30)    |  |  |  |

| リード・データ・バス        | CXRDAT( D0 ~ D31)                   | CXRDAT(D0 ~ D15) |  |  |  |

| ライト・データ・バス        | CXWDAT( D0 ~ D31 ) CXWDAT( D0 ~ D15 |                  |  |  |  |

| リード/ライト           | CXRW(" H ": リード , " L ": ライト )      |                  |  |  |  |

| リード               | CXRS                                |                  |  |  |  |

| ライト・バイト・<br>イネーブル | CXWS(0~3)                           | CXWS(0 ~ 1)      |  |  |  |

| レディ               | CXREADY                             |                  |  |  |  |

(b) M32R ソフト・コア(外部バス・コントローラ経由)

|           | データ・バス                        |           |  |  |  |

|-----------|-------------------------------|-----------|--|--|--|

|           | 32 ビット                        | 16 ビット    |  |  |  |

| チップ・セレクト  | CS(6 ~ 0)                     |           |  |  |  |

| アドレス・バス   | A(25 ~ 0)                     |           |  |  |  |

| データ・バス    | D(31 ~ 0)                     | D(15 ~ 0) |  |  |  |

| リード/ライト   | R/W(" H ": リード , " L ": ライト ) |           |  |  |  |

| リード       | RD                            |           |  |  |  |

| バイト・イネーブル | WE(3 ~ 0)                     | WE(1~0)   |  |  |  |

| レディ       | RDY                           |           |  |  |  |

(d) SH-4A(SH-4/4A)のバイト制御 SRAM モード時

### 表2 アドレス・バスとバイト・イネーブルの動作(MicroBlaze 版,リード/ライト) =

| CPU コアの            | アドレス                    | 8000_0000h | 8000_0000h | 8000_0002h | 8000_0000h | 8000_0001h | 8000_0002h | 8000_0003h |

|--------------------|-------------------------|------------|------------|------------|------------|------------|------------|------------|

| アクセス               | サイズ                     | 32 ビット     | 16 ビット     | 16 ビット     | 8ビット       | 8 ビット      | 8ビット       | 8ビット       |

| MicroBlaze<br>外部バス | Bus2IP_Addr( A0 ~ A31 ) | 8000_0000h | 8000_0000h | 8000_0002h | 8000_0000h | 8000_0001h | 8000_0002h | 8000_0003h |

| (IPIF 経由)          | Bus2IP_ArBE(0 ~ 3)      | 1111       | 1100       | 0011       | 1000       | 0100       | 0010       | 0001       |

| BLANCA             | SYS_Address             | 8000_0000h | 8000_0000h | 8000_0002h | 8000_0000h | 8000_0001h | 8000_0002h | 8000_0003h |

| システム・バス            | SYS_ByteEnable          | 1111       | 1100       | 0011       | 1000       | 0100       | 0010       | 0001       |

図1 バイト・イネーブルのないバスでのバイト単位アクセス

エンコードして 3 ビットを生成し,アドレス・バス A25 ~ A2 には,そのまま外部バス・コントローラの出力するアドレス・バス(M32R の A6 ~ A29)を接続します.そしてアドレス・バスの上位 3 ビットと最下位 2 ビットは,情報がないので常時ゼロとしています( $\mathbf{表}3$ ).

M32Rに限らず,アドレス・バスのLSB側が出力されないというCPUアーキテクチャはほかにもあります.組み込み向けCPUの場合,I/Oピン数の増加はそのままコストに跳ね返ります.少しでも小さなパッケージに組み込んだほうが,低コスト化には有利です.そのため,アドレス・バスのLSB側が削除されることも多いようです.

## SH-3/4 シリーズの場合

SH-3/4 シリーズの場合も M32R ソフト・コアの場合と似ており、リード時にはバイト・イネーブル情報がありません。しかし、M32R ソフト・コアと異なるのは、アドレス・バスがLSB である A0 まできっちり出力されている点です[  $\mathbf{a}$  4(a), (b)].

Interface Mar. 2007