## 第2章 CPLDで入出力を拡張し マイコンで演算処理する

# 簡易整数電卓の設計と製作

内藤 竜治 Ryuji Naitou

本章では、マイコンと CPLD を組み合わせる実例 として、簡単な電卓(写真1、p.139) を製作します。マイコンと CPLD を組み合わせた動作の実験を目的とするため、本格的な電卓ではなく、整数の加減乗除だけができる 4桁の簡単なものとしました。

### 最適な回路の構成を考察する

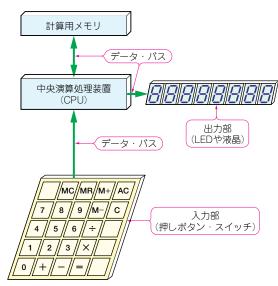

電卓は図1に示した構成で作れるだろうと考えられます。この構成では、スイッチやLEDなどの入出力部と、計算を行う演算部、計算するデータを一時的に蓄えておくメモリ、そして個々の機能ブロック間でデータを伝送するバスなどがあります。これらの構成要素をCPUで作る場合とCPLDで作る場合について、

図1 一般的な電卓の構成

どちらがより有利かを考えてみることにします.

#### 入出力は CPLD が行う

電卓には、数値を入力するためのスイッチや、結果を表示するためのLEDまたは液晶が必要です。しかし、第1章で検討したようにMB-R8CQ基板には汎用 I/O ポートが 11 本しかないので、7 セグメント LED やスイッチをたくさんつなぐことができません。一方、CPLD には I/O ポートは最大で 80 本もあり、LED やスイッチをたくさんつなぐことができます。

I/Oポートの機能で見てみると、R8C/15などのワンチップ・マイコンでは、一つの入出力端子が汎用 I/Oポートやタイマ出力やシリアル通信など、さまざまな役割を兼用していることがわかります。ピン数が少なく多機能なマイコンほど、この傾向は顕著になってきます。

それに対して CPLD は、どの I/O ポートも同じ機能で同じ構造です。クロック信号など一部の例外はありますが、デバイスがもつ端子の機能をほとんど気にすることなく、接続するものを自由に決めることができます。そういう理由から、スイッチや LED などの入出力部品は、CPLD に接続するのが良いといえます。

#### 電卓のための数値計算は CPU で行う

R8C/15マイコンには、16ビットの乗算命令が用意 されています.この命令は長くても6バイトですから、

### Keywords

7セグメント LED,スイッチ,I/O ポート,乗算命令,ロジック・エレメント,レジスタ,マルチプレクサ,SSU,ダイナミック点灯,function 構文,データ通信,R8C/15

# 特集 \* MAX Ⅱ付録基板 徹底活用!

乗算命令を使ってもプログラム ROM の1%にも満たない量です。また、乗算命令の実行時間は、最長で300 ns くらいです。よほどクリティカルな処理を行うのでなければ、CPUのリソースを圧迫することもないでしょう。

ところが、MAXⅡで乗算器を作ろうとした場合、 単純に符号なし16ビット×16ビットの乗算器を作ろ うとすると、528ロジック・エレメントが必要となり、 付録CPLD基板に実装されている240ロジック・エレ メントのCPLDには入りきりません。

CPLDで乗算器を作った場合の動作速度は、QuartusⅡが出力するタイミング・レポートによれば30 ns 程度と、R8C/15マイコンの10倍ほど高速であることがわかります。電卓のようなアプリケーションの場合、マイクロ秒オーダでの応答速度は必要とされませんし、乗算を行っている間にほかの処理をする必要もないので、CPUで計算したほうが良いといえます。

ただし、画像や音声を扱うアプリケーションを作る場合であれば、CPLDに計算をさせたほうが有利になることもあります。目的の処理をCPU(ソフトウェア)で行うか、それともCPLD(ハードウェア)で行うかは、速度やコストや同時実行の必要性などのトレードオフで決まります。必要な処理をハードで行うかソフトで

行うかを決める作業は、システム設計のなかでもっと も面白い部分だといえるでしょう。

#### データの記憶はCPUで行う

CPLDのようにハードウェアで動く回路を設計する場合、データを記憶させることは、しばしとても悩ましい問題となります。

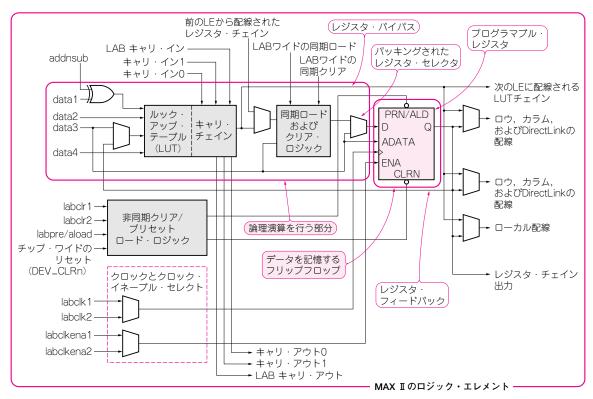

CPLDで1ビットのデータを記憶するには1個のフリップフロップを使用します. しかし、図2に示すように、CPLDの構成要素である「ロジック・エレメント」には、フリップフロップは1個しか入っていませんから、8ビットのデータを記憶するには8個のロジック・エレメントを消費してしまいます.

ロジック・エレメントは、任意のロジックを実現することができる貴重なものです。これをデータ・レジスタのような単純なメモリとして使っても、1個を消費してしまいます。これをもったいないと感じると、CPLDの回路を設計する際に記憶用のレジスタを極限まで節約しようとして、複雑な設計になりがちです。

付録CPLD基板のMAX II CPLD(EPM240T100C5) には240個ものロジック・エレメントがあります.これは一昔前のCPLDでは最大級に相当する規模でしたので、8ビットくらいの記憶ならばそれほど気にしなくてもよいでしょう.

図2 一つのロジック・エレメントには一つのフリップフロップしかない