## DAC PCM1795内部の64倍フィルタと合わせてトータル256倍!

## CDを176.4 kHzで再生! FPGA搭載 USB基板で作る4倍アップサンプラ

第2回 アップサンプラのしくみと作り方

田力 基

Motoi Tariki

本連載では4倍アップサンプラを製作します.

シングル・レート(44.1 k/48 kHz)のPCM 信号を FPGA であらかじめ4倍にアップサンプリングして からD-Aコンバータへ入力します。実験に使用す る USB-FPGA 基板は、本誌 2010年2月号で開発し たものです。これにつながるDAC基板には、テキ サス・インスツルメンツの $\Delta\Sigma$  D-Aコンバータ PCM1795が搭載されています. このICは. デフォ ルトの設定で、入力信号がシングル・レートのとき、 内部の8倍オーバー・サンプリング・フィルタで処 理を行います、さらに何らかの手段で8倍にアップ サンプリングし、トータルで64倍のサンプリング 周波数でΔΣ変調器を動かしています. D-Aコン バータで64倍オーバー・サンプリングされるので. 元信号に対して256倍オーバー・サンプリング動作 していることになり、ノイズの周波数も同じ比率で 高い方へシフトします.

折り返し 雑音を阻止

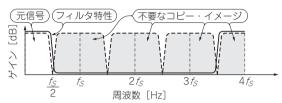

(a) 帯域外ノイズは元信号のスペクトルの複製イメージ

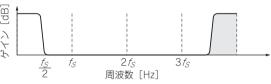

(b) fs /2以上の帯域をフィルタリングする

図1 ディジタル・オーディオの宿命…サンプリング周波数 $f_S$ のn倍の周波数に不要なノイズが現れる

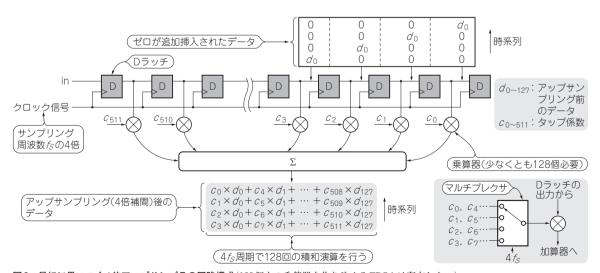

図2 最初に思いつく4倍アップサンプラの回路構成(128個もの乗算器を作り込める FPGA は存在しない) データ・レートを4倍に引き上げるため入力データはあらかじめ1個おきに3個のゼロを挿入する.Dラッチを128段にした上で,右下図のように回路 を工夫すると乗算器を512個から128個に減らせる可能性がある