## 連載

ミキサ/フィルタ/周波数コンバータ··· RF信号処理ロジックの作り方がわかる

## ダイレクト・サンプリング FM SDRの製作

第16回 フルディジタル PLL の FPGA 実装③ PLL で作る FM 復調器の研究

林輝彦 Teruhiko Hayashi

第14回と第15回の2回にわたり、サブキャリアの 生成や復調など、SDRの要所要所に使えるPLL(Phase - Locked Loop)の作り方や動作を考察してきました.

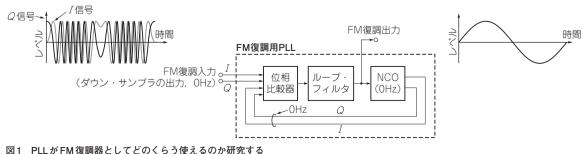

今回は、実際にフルディジタルPLLでFM復調器を作り、FMDDC-3に組み込んでその特性を測定します(図1). 回路規模が大きいCORDICを使ったFM復調回路(本誌2019年10月号で紹介)をPLLに置き換えることができ、性能が十分ならばFPGAのロジック・リソースを節約できます。

Excelを使ってPLLシミュレータを自作し、FM復調器のゲインの周波数特性やフィードバック・ループの安定性、波形のひずみを検討します(本誌ウェブサイトで公開予定). 実際の動作や性能が計算どおりになるのはフルディジタルの大きなメリットです.

FMDDC-3には、今回紹介するPLL方式のFM復調回路は実装しませんでした。理由は後出のとおり、最大許容周波数偏移が不十分だったからです。本稿は、PLLをFM復調器に応用するために必要な技術的課題の研究レポートです。

## 設計の要点

## ● 要点① 回路構成の決定

図2に示すのは、直交2相の複素信号(I/Q信号)を 扱える位相比較器で構成したPLLです。

PLLをFM復調器に利用するときは、位相比較器の入力の片側をFM復調器の入力とし、周波数可変発振器(NCO)の周波数設定入力、つまりループ・フィルタの出力から復調された信号を取り出します。

図2(a)に示すのは、加法定理の式に厳密に従ったフル位相比較器を使ったタイプです。位相比較器から不要な周波数成分(スプリアス)が出ません。

図2(b)は、回路規模の大きいCORDICを使わずに、乗算器2個と加算器1個だけの位相比較器(ミニマム位相比較器)で構成したPLLです、「 $\theta$ が0に近ければ、 $\theta \Rightarrow \sin \theta$ が成立する」という関係を利用して簡素化しています。

今回は、図2(b)のミニマム構成の位相比較器を使ったFM復調器を検討します。図2のPLLはどちらも、周波数選択性のないゲインA倍の乗算器(単純なスケーラ)でPLLの基本特性を調整することができます。LPF特性をもつループ・フィルタを使う必要はありません(コラム A参照).

図1 PLLかFM 復調器としてどのくらう使えるのか研究する 入力はダウン・サンプラが出力する直交2相のI/Q信号. NCOの中心周波数は0 Hz

【セ**ミナ案内】**[ビギナ向け] [実習セミナ] [KIT付き] 実習・GNU Radioで始めるSDR 入門 [教材付き]