## 基板CADで今どき電子工作コーナ

して LTspice や KiCad で始めよう!

世界中のパーツを動かしてカッコいいハードウェア作り!

## 誰でもキマル!プリント基板道場

善養寺 薫 Kaoru Zenyouji

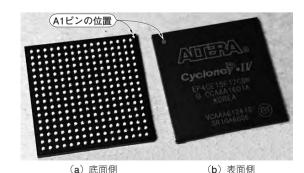

写真1に示すのは、インテル(旧アルテラ)製の CycloneIV FPGA(EP4CE15F17C8N)です。本稿で は、本ICを例に、200ピン超のBGA(Ball Grid Array)配線の基本ルールを解説します。

基板CADにはDipTraceを使いましたが、他の安価・無償CADでも利用できます。

格安プリント基板製造業者PCBWayに依頼する場合,デザイン・ルールの制約から256ピンのBGAパッケージICならばプリント基板の製作が可能です。高機能なBGAパッケージICを搭載したハイエンドな基板製作に挑戦してみませんか. 〈編集部〉

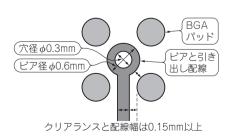

## パッドの隙間にビアを開ける場合, 最小サイズはビア径 0.6 mm/穴径 0.3 mm

図1に示すようなBGAパッケージを搭載する場合、BGAのパッドの隙間にビアを打たなくてはいけません。このビアは小さいほど設計は楽ですが、デザイン・ルール上はそうはいきません。

BGAパッケージもどんどん小型化しています. そのため,数ある製品の中からプリント基板製造業者のルールに適合するパッケージの製品しか使えない制約が発生します.

図2に示すのは、ビア・配線幅・クリアランスの関係です。

格安プリント基板製造業者のデザイン・ルールはほとんど同じです。中国のPCBWayを例にすると、最小ドリル径は $0.3 \, \text{mm}$ 、アニュアリングは $0.15 \, \text{mm}$  (6 mil) です。 つまり、ドリル径 $0.3 \, \text{mm}$ 、ビア径 $0.6 \, \text{mm}$  が最小サイズです。

## ② パッドから配線を引き出す場合,配線幅/ クリアランスの最小サイズは0.15 mm

BGAパッケージのパッドから配線を引き出すときは、パッド間に配線を通します. 配線幅やクリアランスが小さいほど設計が楽ですが、実際の制約上は配線幅とクリアランスともに0.15 mm(6 mil)です. つまりパッド間は0.45 mm以上が必要です.

厳密な話としては、6 milは0.1524 mmです。ガーバ・データ出力時の小数点精度に関わらず、プリント基板製造業者の CAM (Computer Aided Manufacturing) チェックで0.15 mmを6 milとするか、0.152 mmを6 milとするかで別れているようです。0.152 mmとして設計しておく方が無難です。

多くの基板製造業者では配線幅とクリアランスは追

写真1 例題のBGAパッケージIC… $\phi$  0.5パッド, 1 mm ピッチ, 256 ピンの CyclonelV FPGA(4 ンテル)

図1 設計に使用した256ピンのFBGA(FineLine Ball-Grid Array)は、パッド間が1mmあるため配線を通しビアを配置できる参考文献 https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/ds/pkgds.pdf, pp.95-96

【セミナ**案内**】[講師実演] 装置におけるシールド/グラウンド設計法 [講師による実験実 演付き]