パワエレ初心者のための基礎知識と実用ノウハウ

# パワー・スイッチ(MOSFET)の 実践活用技術

第6回 力率改善…ブリッジレス・ブーストPFCの設計

吉岡均 Hitoshi Yoshioka

本文中の\*印がある語句には p.147に用語解説があります.

# 残された電力ロスを改善する

# ● 整流用ブリッジ回路のロスが目立ってきた

電力変換回路の究極効率はもちろん100%ですが、P/N接合の半導体を使用する限りにおいて、これは不可能そうです。しかし回路技術には、例えば降圧型DC-DCコンバータの転流ダイオードをMOSFETに置き換える「同期整流」と呼ばれるものがあります。出力電圧が低いときの電力変換においてはよく応用されています。とくにMPU用VRM(Voltage Regulator Module)などにおいては標準的に使用されています。

#### 一方、AC-DCスイッチング電源では、

- 1次側に使用するパワー・スイッチ(MOSFET) のスイッチングを, 矩形波ハード・スイッチング からソフト・スイッチングに替えることでのロス の改善

- トランスやインダクタにおける磁性材料の改良に よるコア・ロスの改善

- 2次側ダイオードの同期整流によるロスの改善

- 制御ICの利用によって軽負荷時スイッチング周 波数を低下させる省待機電力

### などが利用されています.

そして、効率改善のために残されたもう一つの手が、AC入力の全波整流に使用される「ブリッジ整流ダイオードのロス低減」です。 方々の努力によって電力変換回路各ブロックのロスが改善されてきた結果、AC入力にあるブリッジ整流ダイオードのロスが目立ってきたという訳です。 例えば、ダイオードの順方向電圧降下 $V_F$ が1V、流れる電流が5A(半周期)としても1

本のダイオードで2.5 Wの損失を生じてしまいます.

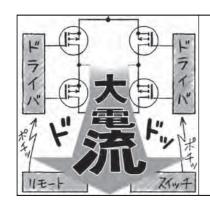

ブリッジ整流ダイオードのロスは、古くからBJTやMOSFETをスイッチとして扱う同期整流技術が提案されていました。しかし、スイッチを4個も使用することになるためコストアップにつながり、実用化はあまり進みませんでした。しかし、近年はPFCの必要性などもあって、ブリッジ整流ダイオードを削除できる回路方式が注目されています。

# ● ブリッジレス・ブーストとは?

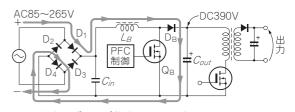

一般的なブリッジ整流+PFC回路の構成を**図1**に示します。この構成では、AC入力電圧を全波整流します。そのためのブリッジ・ダイオードの中で直列となる $D_1$ と $D_4$ 、そしてPFC回路における昇圧ダイオード $D_B$ とで合計3本には電力変換時の電流が通過します。つまり、ダイオード3本分の順方向電圧 $V_F$ によるロスが必ず生じます。

図1 従来のブリッジ整流+PFC回路 ブリッジ・ダイオードのD<sub>1</sub>, D<sub>4</sub>, 加えてPFC回路のD<sub>B</sub>の3 本のダイオードによって電圧降下=電力ロスが生じる

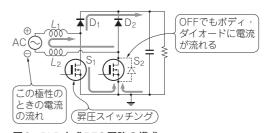

図2 BLB方式PFC回路の構成 2組の昇圧回路によってブリッジ・ダイオードをなくす ことができる、MOSFETのボディ・ダイオードも使用 している